https://e2e.ti.com/support/interface-group/interface/f/interface-forum/647432/tca9545a-issue

器件型号:TCA9545A您好、Sirs、

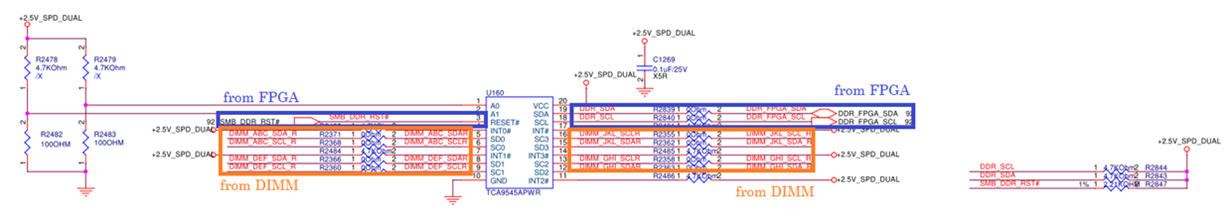

我们将 SMBus 开关 TI/ TCA9545APWR 用于项目 Oceancat 中的存储器。

在某些情况下,我们发现 BMC 无法读取内存的 SPD 信息。

TCA9545APWR 电源正常 VCC 为+2.5V_SPD_DUAL、RESET 为+2.5V_DUAL、序列为+2.5V_DUAL=++2.5V_SPD_DUAL。

从 FPGA 到存储器的 SMBus CLK 和数据通过开关(TCA9545APWR)传输。

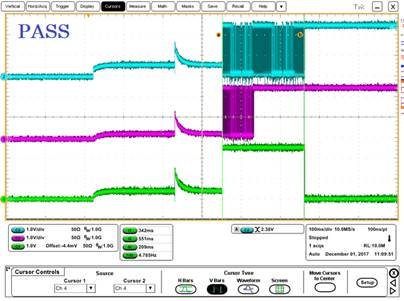

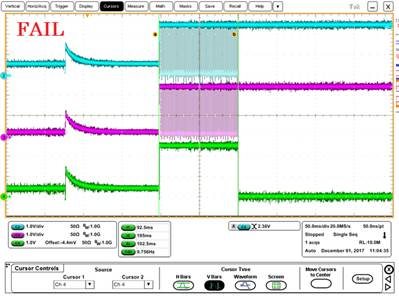

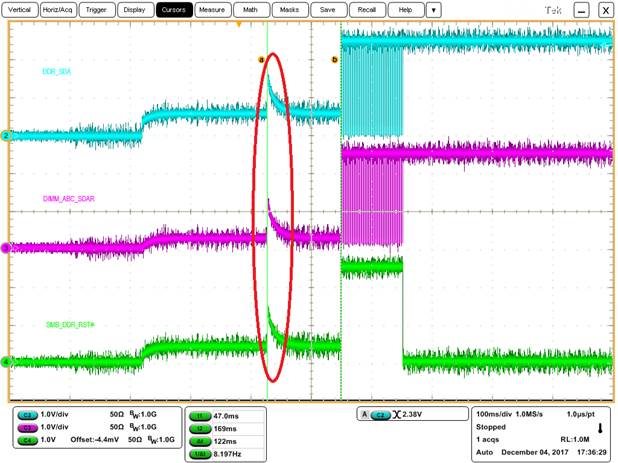

我们在导通平面和失效平面中测量 DDR_SDA、DIMM_ABC_SDAR 和 SMB_DDR_RST#的波形、如以下截屏所示、请参阅。

它显示了故障平面中 SMB_DDR_RST#取消置位的时序短于传递平面。

请帮助我们检查尖峰是否会导致 RST 在早期拉至低电平、从而导致任何异常行为以及 VCC 和 RESET#之间的任何序列

谢谢!!