https://e2e.ti.com/support/interface-group/interface/f/interface-forum/690675/ds90ub948-q1-ds90ub948

器件型号:DS90UB948-Q1大家好、TI 专家、

以下有关 DS90UB948的问题需要您的帮助:

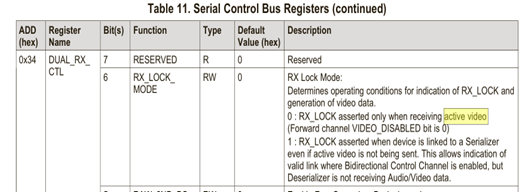

1.电源序列中 T1和 T2的含义是什么~

它 T1用于 VDDIO 延迟时间,T2用于 VDD12延迟时间吗?

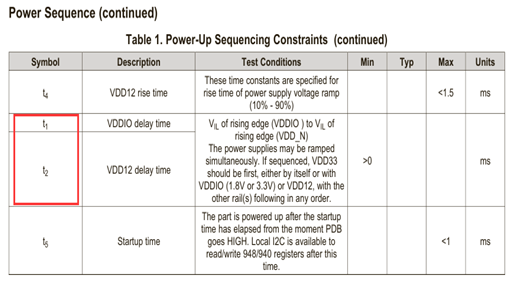

2.How to understand active vedio?If the resolution is wrong,will be a lock signal?(如何理解活动的 Vedio?如果分辨率错误,是否会有锁定信号

图2.

它们的图形是否位于 DS90UB948内部?如果它们没有 LVDS 输入信号、它是否会输出默认图像?

CDC 主机如何通过 HSD 复位 DS90UB948? 是否通过 PDB 引脚?如何实现?

VDDIO 和 VDD33只能,一个 LDO 吗?使用 Bead 隔离它们?

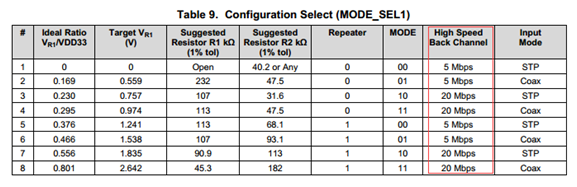

6.它们是 MODE_SEL1中的高速反向通道,这是否意味着 FPDLINK 的传输速率?

图3.

7. PIN1 (锁定)的含义是什么? MCU 应向输出信号反馈什么?

8。PIN4 (BISTC)是否为时钟信号通道?MCU 必须提供参考时钟通道、然后才能进行自检?

对您的~感到很不满意、非常感谢