主题中讨论的其他器件: DS90LV001

顺便说一下、是否有人知道 EN 引脚到底是怎么做的?

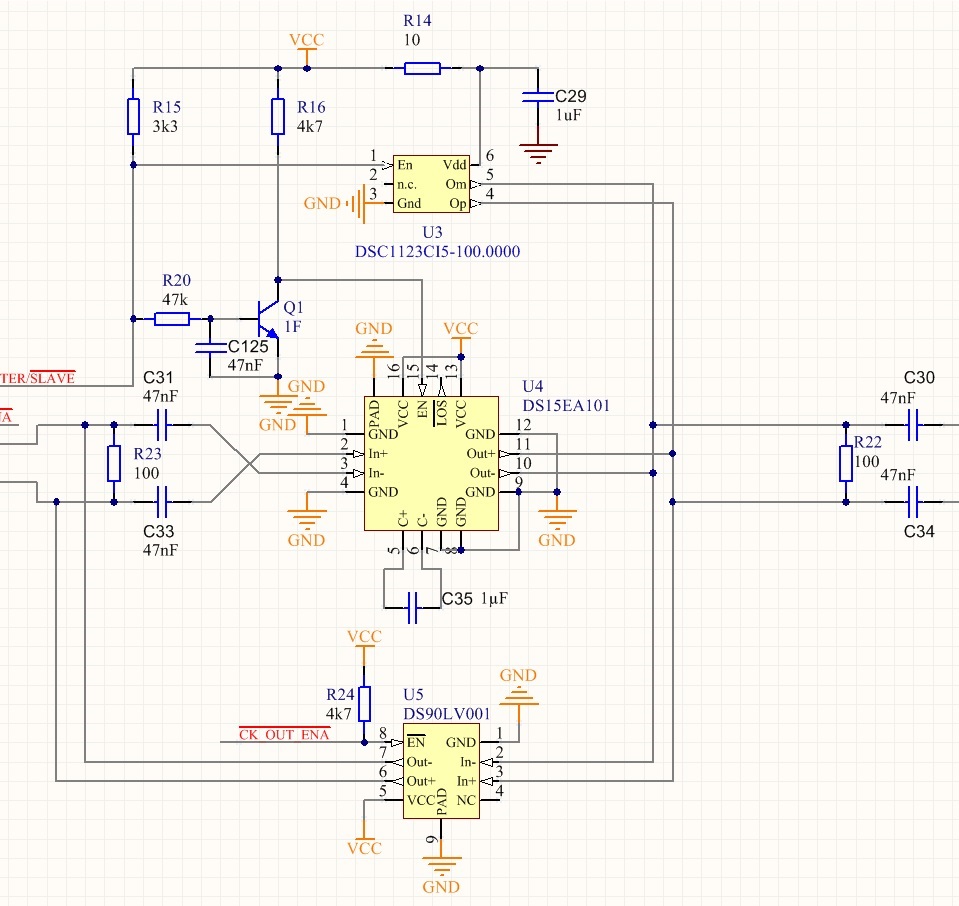

具有2个以电气方式并联的 LVDS 时钟(=线或线)、一个来自 DSC1123 100MHz MEMS 振荡器、另一个来自传入的差分对。

后者在可用和选定时由 DS15EA101进行均衡。

为了进行选择、我管理这两个器件的 EN 引脚、以便更改公共输出线路上可用的源。

我看到的奇怪是叠加在100Mhz 时钟上的低频开/关模式。 当我探测或触摸引脚5&6上的均衡器外部电容器时、它的频率会发生变化。

但 EN 很低! 不应该禁用输出、因此 ds15101对其输出有任何影响?

此外、50欧姆内部拉电阻器在禁用时是否也会保持在该状态?

感谢您的帮助!

弗朗西斯科