请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN65DP159 大家好、我附加了 DP159上电时序截面图。

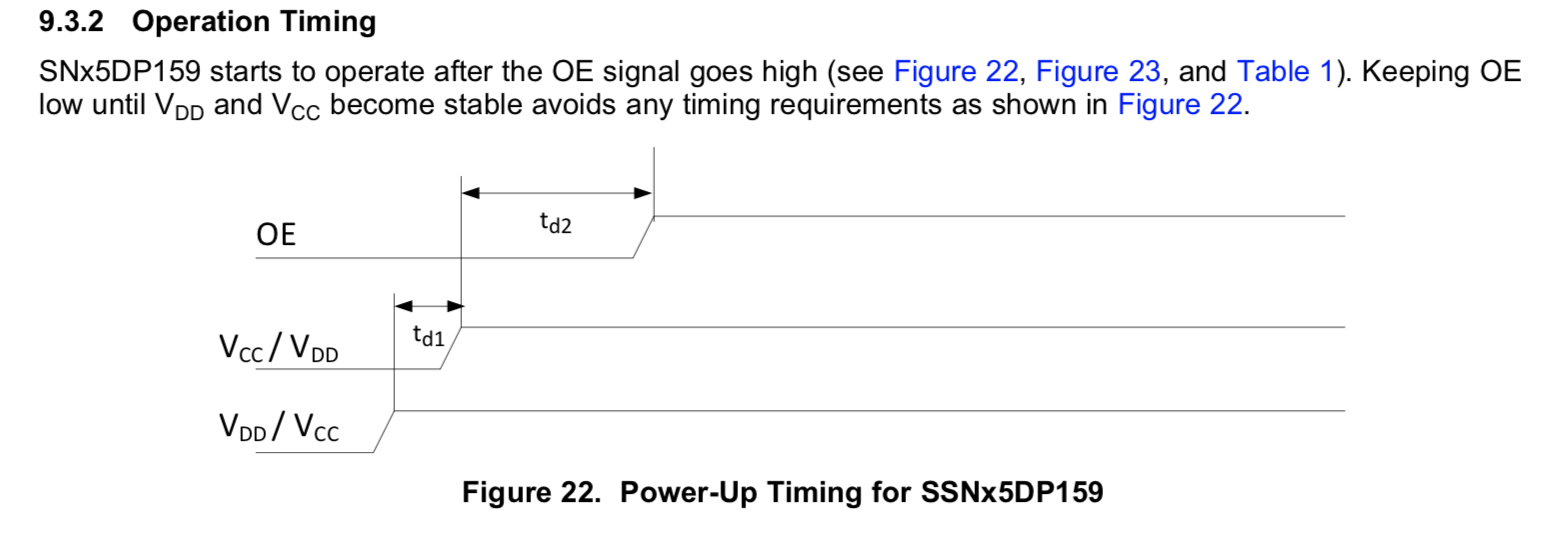

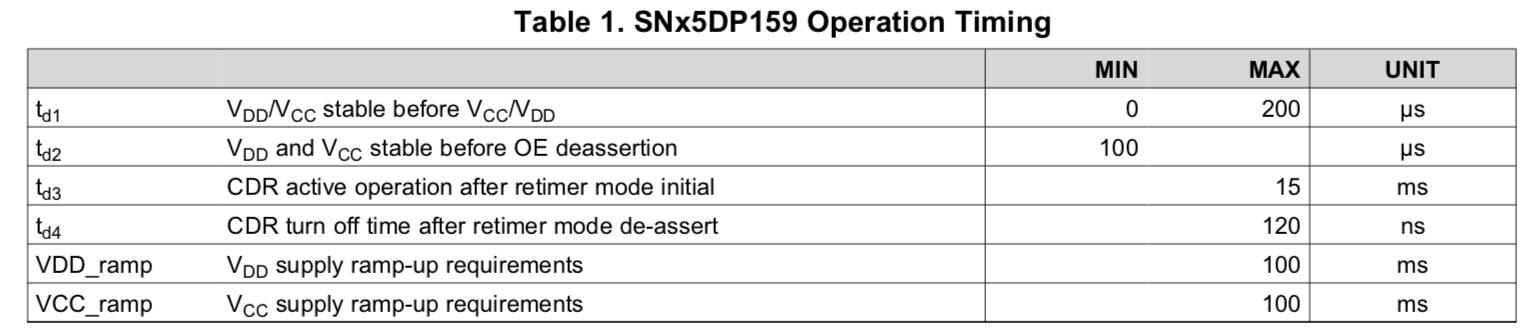

图22让我感到困惑:为什么有 VCC/VDD 和 VDD/VCC? 如何了解 TD1? VCC 和 VDD 上是否存在应首先斜升的特定时序要求?

TD1的额定最大值= 200us。 如果我首先施加 VCC、那么 VDD 必须在200us 内开始斜升?

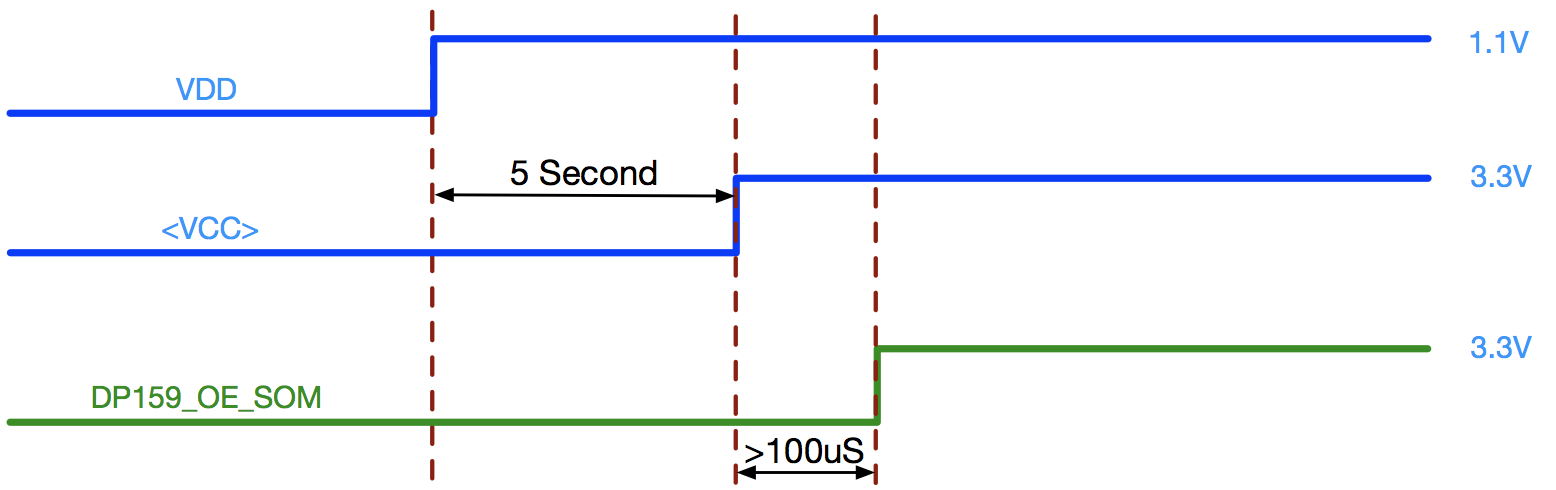

在这个线程中、只要 OE 为低电平、就不需要对 VCC、VDD 排序。

谢谢你。