请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83867CR 您好!

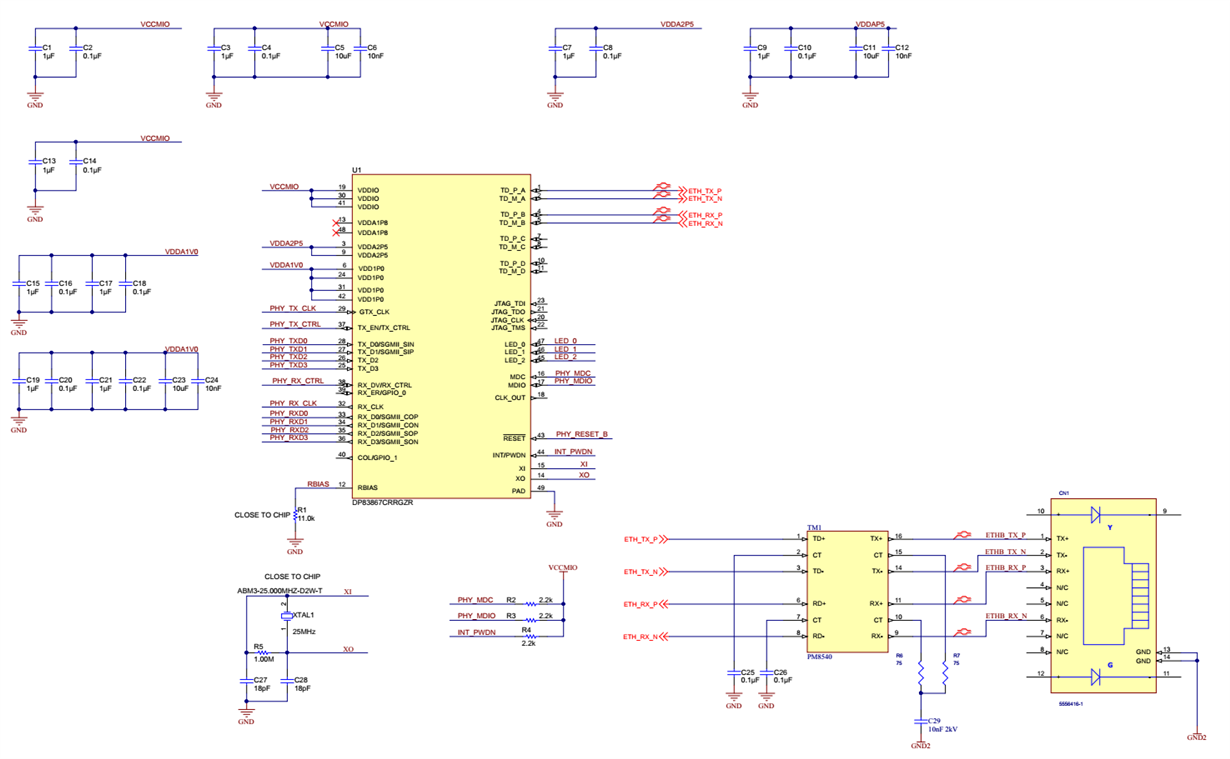

我正在基于 Xilinx 的参考设计进行设计。 我想用 DP83867CR 替换该设计中的 Marvell PHY。

由于某些限制、此设计需要100BASE-TX。 下面是原理图的 PHY 部分。

VCCMIO 为1.8V。 我使用了两个电源配置来避免数据表中提到的电源定序问题。 根据 Zynq 的 PUP 定序要求、上电序列为1.0V->1.8V->2.5V。

我省略了该图中的浪涌保护、但稍后将添加该图。

感谢您对上图的反馈(是否可以? 是否有缺失?)

我有另一个问题、与软件相关。 我在另一个主题(的第二个帖子)中看到  自动协商被禁用。 Linux 驱动程序是否支持此功能? 是否需要进行一些配置或修改才能执行该操作、或者驱动程序在加载时会对其进行处理? 我之所以提出这一问题、是因为我们尝试依赖可用的软件并尽可能保持其原始状态、以避免维护噩梦。

自动协商被禁用。 Linux 驱动程序是否支持此功能? 是否需要进行一些配置或修改才能执行该操作、或者驱动程序在加载时会对其进行处理? 我之所以提出这一问题、是因为我们尝试依赖可用的软件并尽可能保持其原始状态、以避免维护噩梦。

提前感谢您。