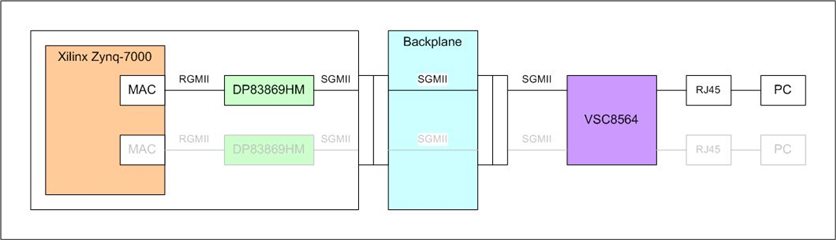

我们使用 DP83869HM 在 RGMII 和 SGMII 之间建立桥接。

DP83869HM 的 RGMII 侧 连接到 Xilinx Zynq-7000集成 MAC。 SGMII 端通过背板连接到包含 VSC8564 的电路板(将 SGMII 转换为1000BASE-T)。

这种排列的两个实例被执行(见下文)、但一个实例当前正在调试中(另一个实例在下面灰显、但其相关性在后面给出)。

首先初始化 VSC8564、然后是 DP83869HM。 DP83869HM 通过自举配置配置为所需模式。

DP83869HM 的寄存器访问序列如下所示。 从 BMCR 开始的行是最相关寄存器的打印输出。

寄存 器访问用一些文本进行描述、然后是什么是访问、例如 PHY_TI_CFG4 (ermw[0x0031]&= 0xFF7F)是对寄存器0x31的扩展读取-修改-写入访问、使用0xFF7F 对值进行与修改以修改读取的值。

BMCR[0x0000]=0x0140 BMRS[0x0001]=0x794D SGMIIA否定 状态[0x0037]=0x0003 OPTMODEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDE[0x0043 FiberControl[0x0C00]=0x1140 FiberStatus[0x0C01]=0x617D

SW 重新启动(RM瓦[0x001F]|= 0x4000)

MII 复位(RMW[0x0000]|= 0x8000)

延迟

设置 PHY_CTRL (w[0x0010] 0x5048)

设置 RGMIIDCTL (EW[0x0086] 0x0077)

设置 RGMIICTL (EW[0x0032] 0x00D0)

RX_CTRL 不是自举模式3或4时、针对不稳定链路的软件权变措施

PHY_TI_CFG4 (ermw[0x0031]&= 0xFF7F)

Aneg Adv (RM瓦[0x0031]|= 0x0DE0)

Aneg Adv (RM瓦[0x0009]|= 0x0300)

负极触发(RM瓦[0x0000]|= 0x1200)

正在等待 PHY 完成自动协商。

BMCR[0x0000]=0x1140 BMRS[0x0001]=0x794D SGMIIA否定 状态[0x0037]=0x0003 OPTMODEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDE[0x0043 FiberControl[0x0C00]=0x1140 FiberStatus[0x0C01]=0x6179

BMCR[0x0000]=0x1140 BSRM[0x0001]=0x794D SGMIIAegStatus[0x0037]=0x0001 OPTMODEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDEDE[0x0043 FiberControl[0x0C00]=0x1140 FiberStatus[0x0C01]=0x617D

最后两个寄存器状态输出相距一秒、最后一个寄存器状态重复读取相同的时间长达30秒、没有变化。

可以看出链路状态报告为链路启动(BMSR 位2)、自动协商过程报告为未完成(BMSR 位5)、但未指示远程故障(BMSR 位4)。

但是、光纤状态寄存 器也会报告链路打开(FiberStatus 位2)、但自动协商过程会报告为完成(FiberStatus 位5)、但会指示远程故障(FiberStatus 位4)。

不清楚哪一个与 RGMII-SGMII 桥接模式相关、但两者都表示存在问题。 感谢您在解决此问题方面提供的帮助。

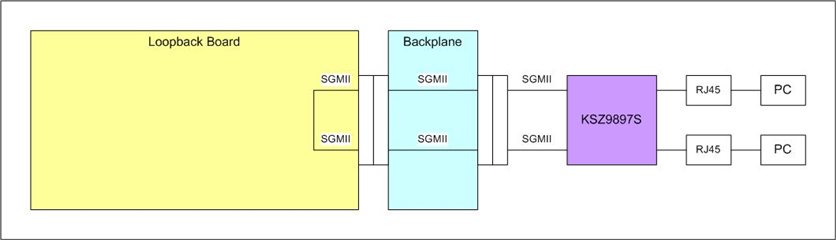

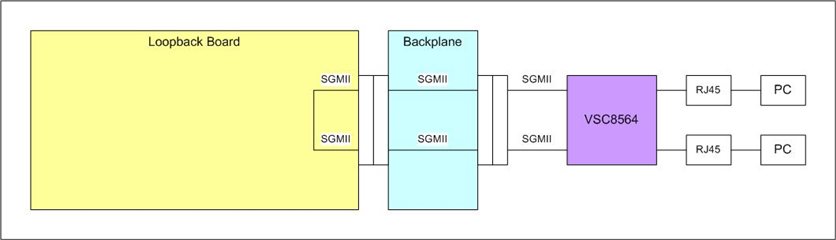

背景:电路的背板/VSC8564/PC 部件已在将 SGMII 环回插入背板的情况下进行测试(如下所示)。 SGMII 链路成功自动协商到1G、两台 PC 可以彼此 ping 通。 因此、假设 SGMII 链路在 PCB 布线阻抗等方面正常、并且 VSC8564设置正确。