你好。

我正在为 STM32F769开发一个应用、它具有双通道 DSI 主机、将连接到1024x600 18bpp LVDS 面板。

我设法使面板工作并在其上显示测试模式、但无法从 MCU 获取任何图像。

在开发此应用时、我首先使用 DSI 转 HDMI 适配器、代码经过调整、分辨率为1024x600、在42.3Hz 时正确显示、DSI 速度为每通道400Mbit/s、非突发模式下显示同步脉冲。 这样、我就知道 DSI 流在工作。

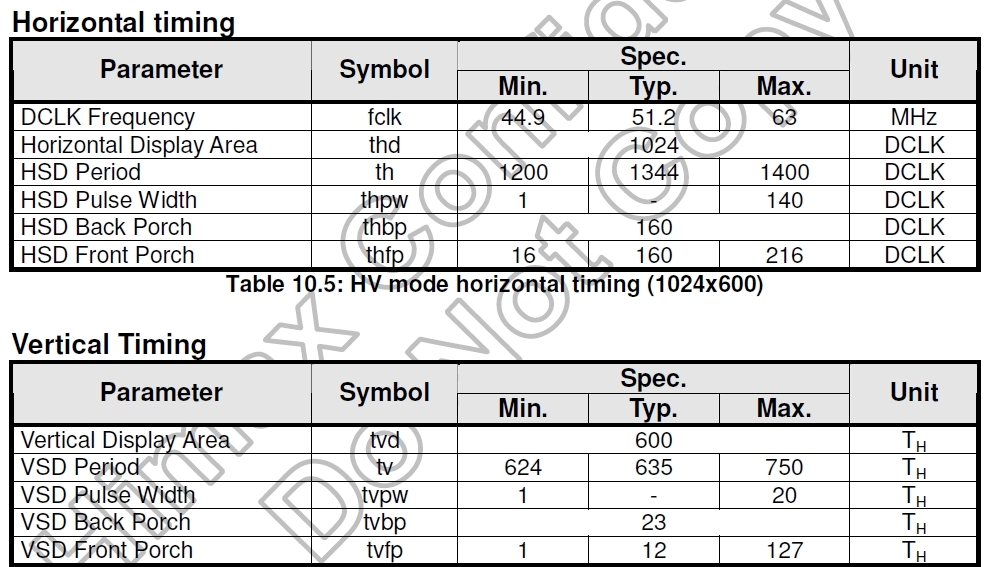

已在各种时钟速率下测试面板、并且应该能够使用大约25MHz 的时钟频率在该刷新速率下工作

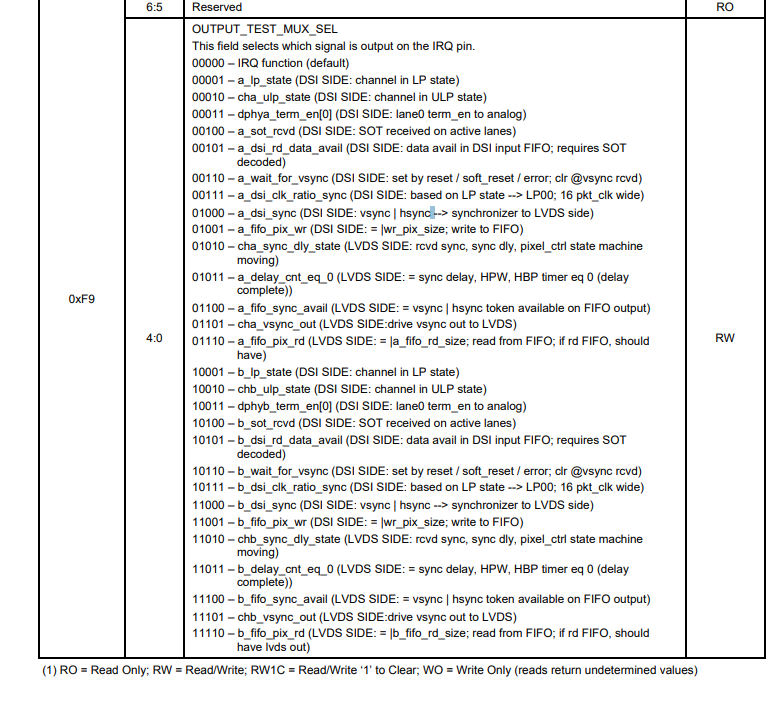

当调试 SN65DSI83时、我发现 LVDS 流从未启动、它会生成同步错误中断(寄存器0xE5的位7一直被置位、即使我将其清零)

LVDS 时钟由 DSI 时钟生成、我确保 DSI 时钟是连续的、没有 PLL 错误。

此外、还会检查启动序列、以便当 EN 置为有效时、LP11中的所有通道都处于置位状态、20ms 寄存器设置完成后、视频流将启动、之后 PLL 将启用、并向 SN65DSI83发送软复位信号

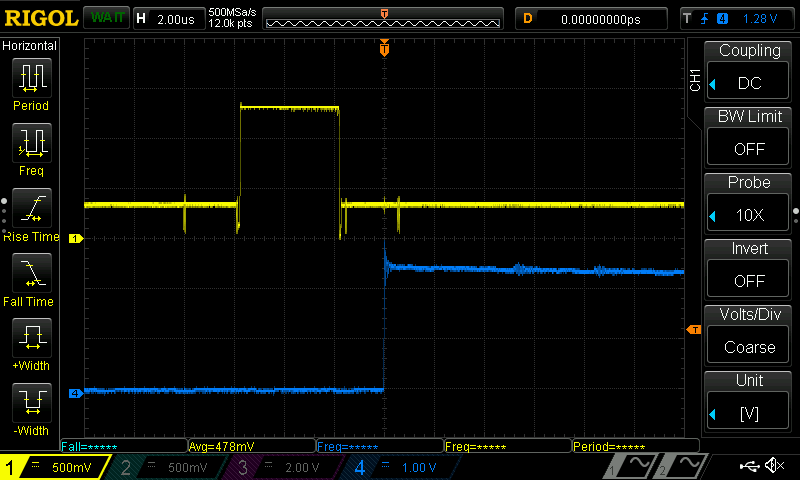

导致此同步错误的原因可能是什么? 它在流启动后立即显示、IRQ 线路已配置、并且在启动流后立即变为高电平。 当启动 PLL 时、它也会被清零、并在下一帧开始时再次变为高电平。

我已使用 DSI 调谐器检查设置、该设置应该正常、最小时钟为150MHz、系统设置为200MHz (400Mbps)

感谢你的帮助。