您好!

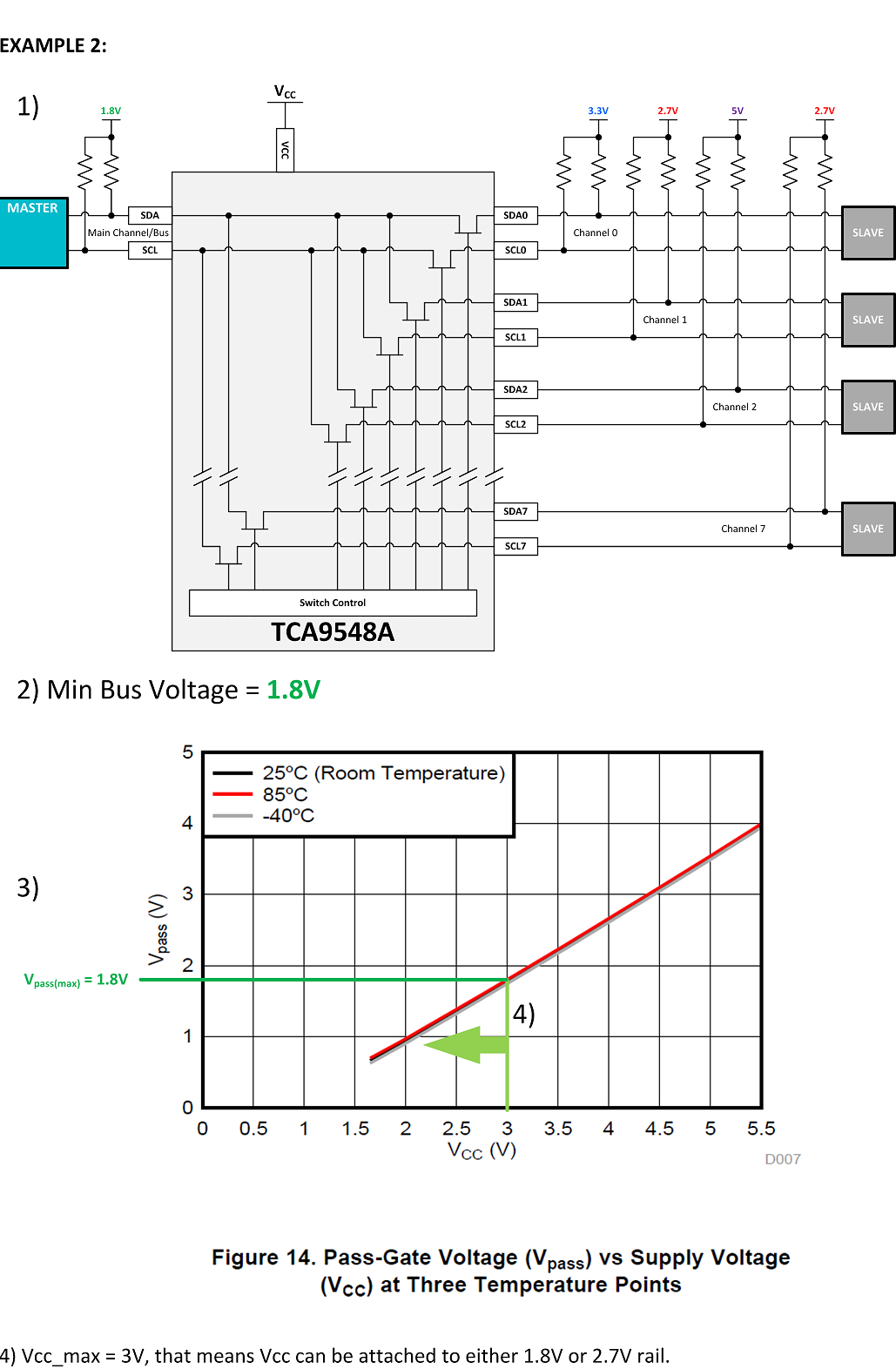

我对具有1.8V 主器件和3.3V 从器件的 TCA9548A 上的适当 VCC 有疑问。 VCC 为2.5V。 我使用了以下帖子中的示例2来设置该电压。

我的理解是、2.5V 可以。 不过、在查看设计时、我发现对于 A0-A2、SCL、SDA 和/RESET、VIH 为0.7 x Vcc (数据表的表6.3)。

现在、0.7 x 2.5V 是1.75V、这太接近主器件的1.8V。

首先、我想知道我在这项分析中缺少什么。

另一方面、我想知道如果我将 VCC 设置为1.8V、是否会降低性能、因为这样我就可以省去/RESET 线路的电平转换器(1.8V > 2.5V)。

提前感谢。