主题中讨论的其他器件: DS92LV18、 DS25BR120

DS25BR110用于均衡/缓冲 LVDS 串行器/解串器信号、该信号在经过几米的 CAT5e 电缆布线并将输出馈送到解串器后。

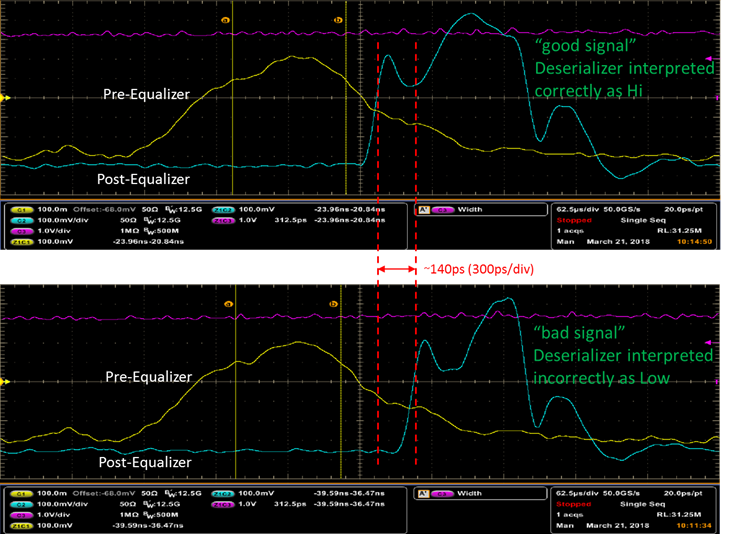

以下示波器捕获显示了进入和输出 DS25BR110的串行数据。 示波器与解串器的 RCLK 同步。 请注意、输入信号看起来类似、但"不良"输出的输出在前沿具有140ps 的延迟。 脉冲计时结束相同 、这似乎是二进制事件、要么是正确的、要么脉冲缩短了140ps。

导致这种离散移位的原因是什么? 假设均衡器用作模拟滤波器、然后是 LVDS 驱动器以恢复 LVDS 信号电平和边沿速度。