Other Parts Discussed in Thread: LMH1983, LMK03328

主题中讨论的其他器件: LMK03328

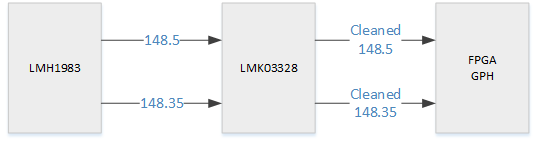

现在、我们还有一个与 LMH1983和 Xilinx Ultrascale FPGA 一起用于12G-SDI 输入和输出的项目。

由于 LMH1983 (PLL2和 PLL3)的性能不符合 Kintex Ultrascale FPGA 规范、因此我还计划添加 LMK03328以实现抖动清除。

我想确保能够同时为 PLL2和 PLL3输出时钟使用单芯片 LMK03328。

非常感谢!