Other Parts Discussed in Thread: SN65MLVD206B

几年前、有人问、当发送https://e2e.ti.com/support/interface-group/interface/f/interface-forum/126882/help-with-noise-on-a-half-duplex-m-lvds-line节点上的 DE 从高电平转换为低电平时、接收节点的接收输出引脚上会出现毛刺脉冲。 Earl Close 的最后一篇文章描述了我与 SN65MLVD206B 完全相同的情况。 我的设置完全相同。 我的总线电缆是100欧姆屏蔽双绞线、两端都有100欧姆端接。 *RE 在所有节点上永久置位。

当节点完成传输时、数据为逻辑低电平(这是我们的停止位)。 当 DE 失效(从高到低)时、我们会在总线上的其他节点的 R 引脚(应为逻辑低电平)上看到非常短暂的毛刺脉冲。 在 DE 转换时、我们看到 A 线和 B 线都开始转换到浮动状态、但在很短的时间内、A 上升到略高于 B、从而导致 R 引脚上出现逻辑高毛刺脉冲。 我们尝试在总线上添加一个电阻器偏置网络、以便在空闲期间将 A 拉低和 B 拉高、但我们发现必须在器件 A 和 B 引脚的每个节点上实现这一点。

只是想重新发布该问题、看看是否有任何关于可能发生的情况的建议。

下面是在现在关闭的主题中发布的原始问题:

我遇到的问题与 Luis 完全相同。 我使用的是65MLVD206、并简要尝试了65MLVD201、看看它是否更好。 我的设置在一端有一个发送器(通过 TE 打开和关闭)、10cm 传输线、在另一端有一个接收器 *RE 在两端都连接到低电平。 每一端都有一个100 Ω 终端器。 我需要接收端的 R 与发送端的 D 完全相同 我将向您展示我在示波器上找到的内容:

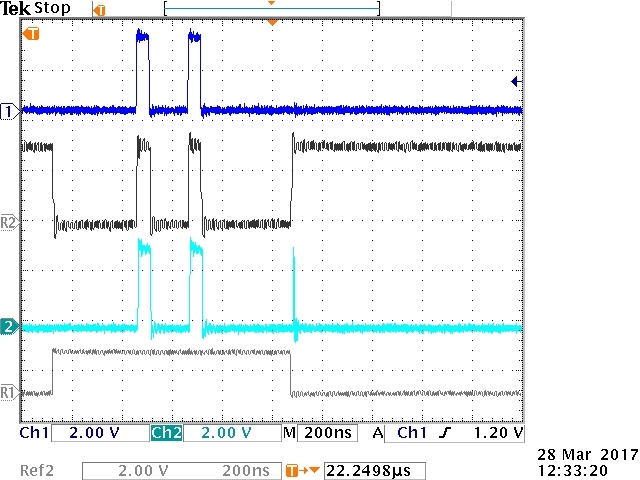

1:发送65MLVD206时 D 处的信号

R2:接收65MLVD201时 R 处的信号(实际上不可用)

2:接收65MLVD206时 R 处的信号(当 TE 关闭时会出现毛刺脉冲)

R1:发送65MLVD206时、DE 上的信号

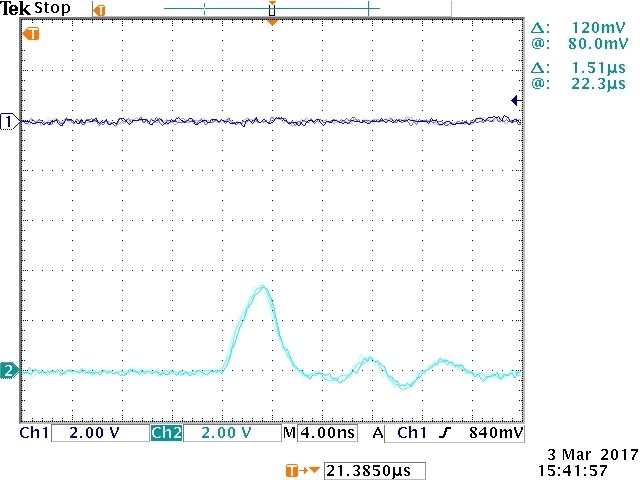

放大 R 线(底部波形)上的干扰:

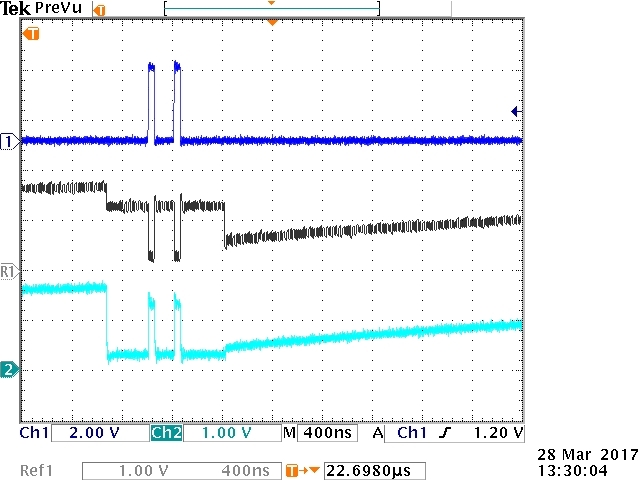

并查看 LVDS A 和 B 线路:

1:发送65MLVD206时 D 处的信号

R1:接收65MLVD206时 B 处的信号

2:接收65MLVD206时 A 处的信号

由此您可以看到 LVDS 信号的行为。 当 TE 关闭时,B 信号快速下降,A 线稍微向上移动,但仍是 B>A,因此我们不应看到1输出。

如果我使用50欧姆的端接而不是100欧姆、问题就会消失。 我也可以像路易斯那样偏置、但这似乎是根本错误的。 我需要一个强大的解决方案、我担心这是一个带辅助解决方案。

您是否能够解释发生了什么情况? 接收器是否具有一定的电感、以便当 B 在上升时快速下降、并将其视为1时、即使电压电平不足以证明这一点?

谢谢、

耳塞