https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1188936/ds16f95-no-connect

器件型号:DS16F95如果未使用、差分输入是否可以保持开路? (或者它是否需要连接至低电平或高电平)。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1188936/ds16f95-no-connect

器件型号:DS16F95如果未使用、差分输入是否可以保持开路? (或者它是否需要连接至低电平或高电平)。

您好、Nikhil、

具体取决于应用。

在 TX 模式下、A/B 引脚可以保持悬空、因为它们是输出-但是输入应该被拉至已知的逻辑电平、这样 TX 引脚就会振荡并且有可能从开路引脚辐射能量。

在器件的 RX 模式下、如果未使用、A/B 引脚不应保持开路/悬空。 A 和 B 之间的电压需要>= 200mV 或<=-200mV、否则输出引脚可能会产生干扰、因为 A/B 引脚上的逻辑电平是不确定的。 如果未使用的 A 或 B 需要上拉为高电平、并且 B 或 A 需要下拉为低电平、以便差分电压处于已知的有效逻辑电平。 以防止输出(RO)引脚上出现毛刺脉冲。 因此、为了使 RO 具有逻辑一输出 A 为高电平、B 为低电平、并且如果 RO 将具有~Ω GND 的输出、那么 A 应该被拉至低电平、B 应该被拉至高电平。

如果您有任何其他问题、请告诉我、我将看到我可以做什么!

最棒的

Parker Dodson

您好、Nikhil、

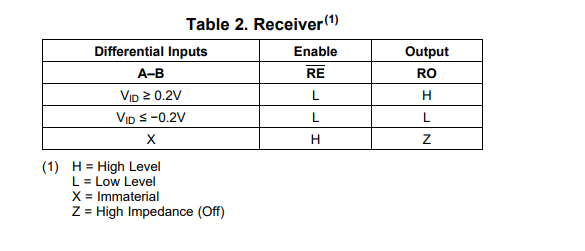

对于差分总线输入、请参阅表2 (第2页)-驱动器无关紧要、因为未使用的输出可以保持悬空而不用担心。 但是、由于这是半双工 A、B 也可以是接收器

VID 额定值仅定义为高于200mV 和低于-200mV -在这些阈值之间输入处于不确定 的逻辑状态(这是隐含的、但未明确说明) -这意味着"R"引脚可以是高电平或低电平-或者在两者之间随机切换。 如果总线上存在终端、则在本应用手册 https://www.ti.com/lit/an/slyt324/slyt324.pdf 中详细介绍了设置总线上空闲电压的计算方法

如果没有端接-将 A 拉至 VCC 和 B 拉至 GND 将 VAB 电压设置为~VCC、当器件处于活动状态时、该电压将在"R"引脚上注册为逻辑1、并且您具有已知的逻辑。 由于"R"是一个输出并且不会产生干扰、因此如果未使用它、它可以保持悬空。

对于 DE、/RE 和 D 输入引脚、其未在数据表中明确说明-它们通过驱动器电气规格下的 VIH 和 VIL 额定值(对于第4页上的引脚 DE 和 D)来表示 、其中 VIL 和 VIH 分别为最大0.8V 和最小2.0V。

对于/RE 引脚、VIL 和 VIH 与驱动器逻辑引脚相同(VIL 最大值为0.8V、VIH 最小值为2.0V)、额定值如第6页所示。

由于存在逻辑状态不确定的电压范围(0.8V < Vin_不确定< 2.0V)、此时如果这些引脚悬空、未使用的输入会导致这些引脚上的毛刺脉冲+ A/B 输出上的毛刺脉冲。 这是此器件或这些类型的器件所特有的-这是未使用的 CMOS 电路输入的常见潜在问题,这就是为什么没有明确说明的原因-请参阅应用手册,详细说明可能的负面影响: https://www.ti.com/lit/an/scba004e/scba004e.pdf?ts=1674588172196&ref_url=https%253A%252F%252Fwww.ti.com%252Fsitesearch%252Fen-us%252Fdocs%252Funiversalsearch.tsp%253FlangPref%253Den-US%2526searchTerm%253Dfloating%2Bcmos%2Binputs%2526nr%253D9051

如果您有任何其他问题、请告诉我

最棒的

Parker Dodson