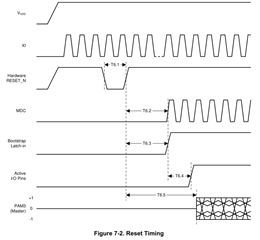

在 DP83TG720R-Q1数据表中,它定义了以下复位时序:

我们有以下问题:

a) VDD 是否包含图中 VDDA VDDIO VDD1P0的所有电源?

b) VDDA VDDIO VDD1P0电源 PHY IC 的哪个模块? 如果 VDDA 和 VDDIO 先出现、VDD1P0稍后出现、或者 MCU 复位导致 VDD1P0电压降低然后升高、这将对以太网通信的建立产生影响?

c)自举锁存的具体功能是什么? 它是否通过 STEL_1引脚(PHY IC 的第14引脚)进行控制?

d)如果 DP83TG720第一次初始化失败,PHY 芯片是否可以再次支持重试初始化? 如果是、当再次重试时如何配置它?

e)在上电时序期间、是否也需要通过 MCU SW 配置硬件 RESET_N 引脚、方法与复位时序相同?