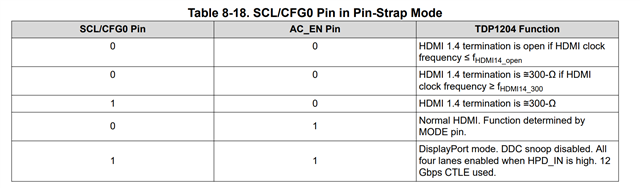

主题中讨论的其他器件:DS125BR820、 TDP1204、TMDS1204

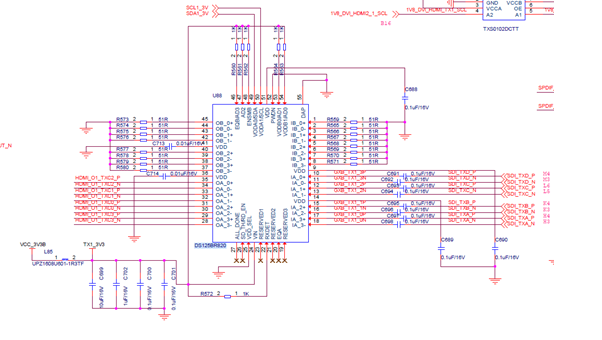

我们使用 DS125BR820作为 HDMI2.1 TMDS/FRL 输出的转接驱动器、上图是 SCH。

DS125BR820的主要寄存器设置如下:

RDEXT = 0x08;

EQx = 0x00;

VOD = 0xa8+6;

VOD_DB = 0x00;

SD_TH = 0x00;

DS125BR820的输入是 HDMI2.1 TMDS/FRL 输出、这些输出来自 Xilinx ZU7EV 的 FPGA。 DS125BR820的输出 用作"HDMI"源。

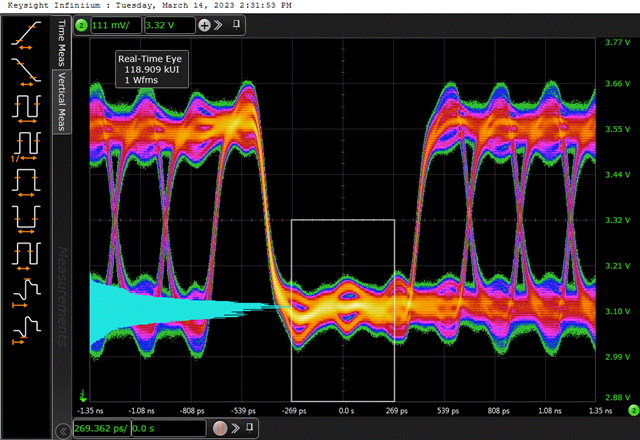

根据 TMDS 原理、TMDS 信号应由恒流源(10mA)驱动。 由于在 HDMI 的接收端、TMDS/FRL 信号会被拉高至3.3V 且阻值为50欧姆。 如果 TMDS 信号 Vpp 为500mV、则 TMDS 正常输出的高电平应为3.3V、而低电平应为2.8V。

由于 DS125BR820也是 CML 输出、因此输出应 符合 TMDS 原则。

DS125BR820的输出中。 TMDS 的 DS125BR820输出高电 平为3.55V、低电平 约为3.1V 。 请参考图片。

问题: DS125BR820是否存在任何寄存器设置或 SCH 问题? 我们应用中 DS125BR820的 TMDS 电平 与正常 TMDS 输出不同、为什么?

感谢您的大力支持!