Other Parts Discussed in Thread: DS15BR400

主席女士/先生,

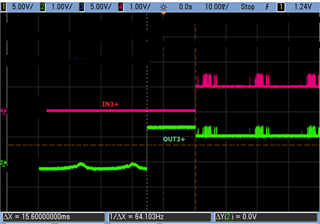

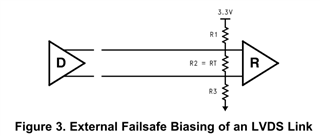

对于 DS15BR400、在其加电并启用后、可以发现当 IN+(~0V)没有任何输入时、OUT+将输出~1.8V、具体请参阅下文。 是否有任何方法可以将输出与 IN 同步?

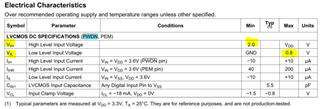

另一方面、我们希望使用 RC 来延迟 PWDN#的拉高。 对于控制 PWDN#、根据技术规格、VIH=2.0V 最小值、VIL=0.8V 最大值 PWDN#是否有任何上升时间/下降时间要求? 谢谢!

此致、

Eric Li