请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TUSB1210 您好!

我在 FPGA 板中使用 TBSU。

现在尝试使用 TBSU Phy 芯片在 FPGA 中测试我的 RTL

(此时 FPGA 将输出时钟发送到 TBSU )

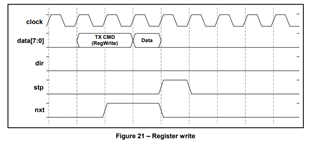

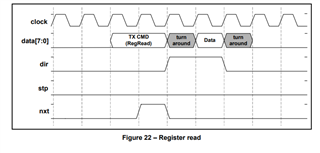

能否查看读/写时序图?

它在 FPGA 端的单个按钮中与 ULPI 时序不匹配。

我认为这可能与读取相关、但 DIR 很早很长一段时间才会出现脉冲。

1) 1)我需要 wave form 进行读取/写入

2)我需要这个模拟模型