请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DS125BR401 早上好!

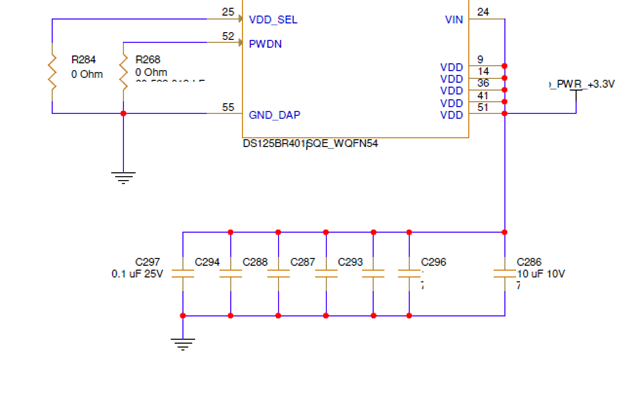

我当时在看老设计、发现电源设计很错。 从提供的屏幕截图中可以看出、 VDD_SEL 连接到 GND。 根据数据表、将此引脚接地将启用内部 LDO、从而提供2.5V 的稳压输出。 此外、根据数据表、如果我为 IC 提供一个3.3V 电源轨并通过 VDD_SEL 启用内部 LDO、则应使用一个0.1uF 的本地旁路电容器将 VDD 引脚单独连接起来... 但是、正如您在提供的屏幕截图中看到的、在启用内部 LDO 的情况下、+3.3V 电源轨也连接到 VDD 引脚。 奇怪的是、它似乎对 IC 没有太大影响... 使用 VDD 引脚的绝对最大额定值(2.75V)进行验证后、我想知道芯片为什么不起炸或者对 IC 产生任何影响。

我是否遗漏了有关这种特定电源拓扑的信息? 我认为上述设计错误会对您造成什么影响?

此致