你好

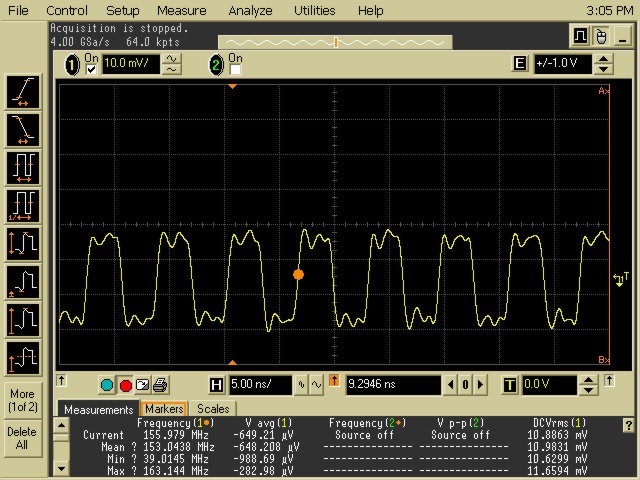

在我的 TLK10232设计中、我注意到了可能是重合或可能意味着:当 REFCLK 输入由稳定的 CO 驱动时、PHY 正常工作、流量流动。 当 REFCLK 由来自 FPGA 或 DPLL 的时钟驱动时、PHY 无法正常工作(存在连续数据错误)。 我已经测量了所有情况下的时钟输入、所有时钟都没问题。 不同之处在于、上电后时钟不会立即出现(上电后、DPLL 和 FPGA 都配置了明显延迟)、便会出现问题。 但是、在所有情况下、复位都会在应用时钟后生效。 那么、上电时钟延迟是否会导致此类问题?