https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1227639/dp83826e-dp83826e

器件型号:DP83826E您好!

我们的此设计基于 DP83826ERHBT

硬件端:

原理图:

e2e.ti.com/.../Ethernet-_2D00_-DP83826E.pdf

布局:RMII 布线长度

我们 在 RMII 线路上有终端电阻器、

如果我们有任何 布局问题,您能提供建议吗 ?

所有线路50欧姆控制阻抗

布线长度如上图所示

软件方面:

我们在电路板上做了一些测试、

我们在 PHY 和 PC 之间进行了环回 ——在 负载测试下运行良好

我们在 MAC 到 PHY 之间执行了环回--我们丢失了数据包

我们在 将 DP83826连接到 Xilinx zc7000系列(7030)时遇到问题。

MAC 似乎并未捕获所有接收到的数据包(Rx 数据包)。

为了排除任何与电缆相关的问题、我已断开以太网电缆连接并将 PHY 置于数字环回模式(0x16=0x104)。

即使在这种配置下、仍然会发生数据丢失。 作为验证测试、我将 MAC 本身置于回路模式、然后测试仪成功识别所有数据。

就接收停止前发送的数据量而言、数据丢失的发生不遵循一致的模式。

它可能在一秒钟后发生、甚至在几分钟后发生。 在忽略任何传入数据几分钟后、它将再次开始接收、直到下一次接收中断。

有趣的是、我在以太网链路完全建立时观察到相同的行为。 MAC 接收几个数据包、然后在一段时间内暂停接收过程(同时仍在发送数据)、

并最终恢复接收。

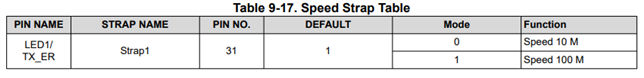

我还使用10M 和半双工设置进行了环回测试、但结果保持一致。

我附上了 MII 寄存器供您参考。 但是、我不认为这是问题的根本原因、因为信道在大约60%的时间内正常工作。

我怀疑 MII 设置对这种行为负责。

此外、TI 提供的 Linux 驱动程序(u-boot、kernel)也存在问题

连接的寄存器转储

e2e.ti.com/.../8lab_5F00_ti83826Registers.txt