大家好、

我们计划将 LAN7431 (PCIe 转 RGMII 芯片)与 TI 的 DP83TG720R (RGMII 转1000BASE-T1) PHY 芯片连接。

在设计分析阶段、我们想澄清下面提到的几个问题、

问题1: 检查 LAN7431和 DP83TG720R 的直流分析后、LAN7431作为输出、DP83TG720R 作为输入的噪声容限高值为0V。 您能否告诉我们、这是否是我们必须考虑的问题? 我附上下面的直流分析表供您参考。

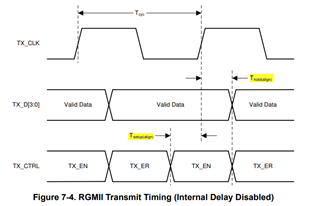

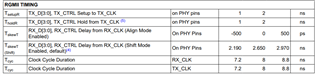

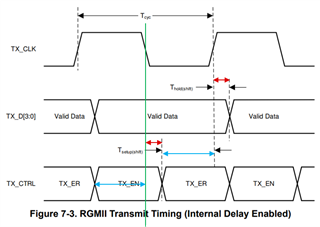

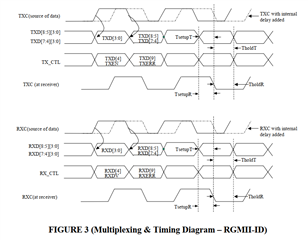

问题2. 在对 RGMII 接口进行时序分析时、在 DP83TG720R 时序图中、时钟下降沿的输出没有变化。 但根据作为 DDR 接口的 RGMII 接口、数据在时钟的上升沿和下降沿传输。 您能否告诉我们、数据保持稳定所需的设置时间以及如何在 DP83TG720R IC 中处理数据。

来自 RGMII 规范的图像

图像 、请告知我们数据将如何在时钟的下降沿出现?

谢谢

Dharaneshwar S