主题中讨论的其他器件: DS90UB953-Q1

尊敬的团队:

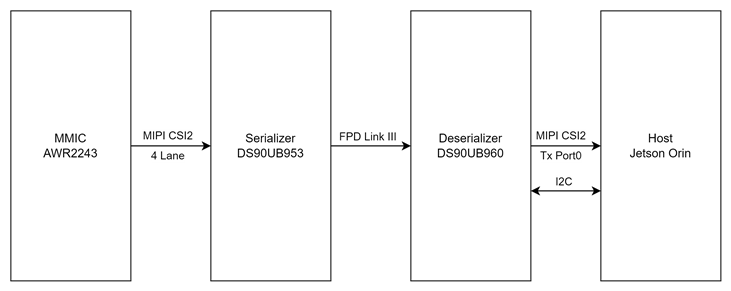

我们将 DS90UB953-Q1和 DS90UB960-Q1用作串行器/解串器、 通过 MIPI CSI-2接口传输来自传感器的视频流。 我们只连接一个传感器、并将线路输出设置 为 DS90UB960 CSI2端口0。

但是、我们无法从端接侧读取视频流、并且端接的 D-PHY 会出现"LP 序列错误"。

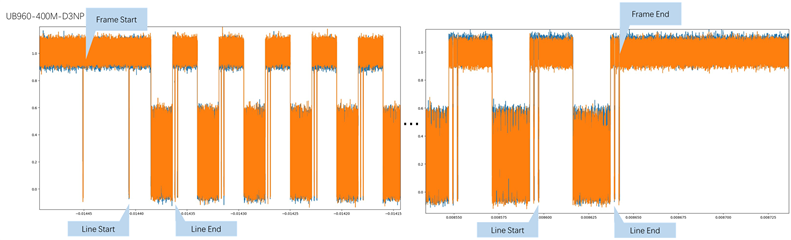

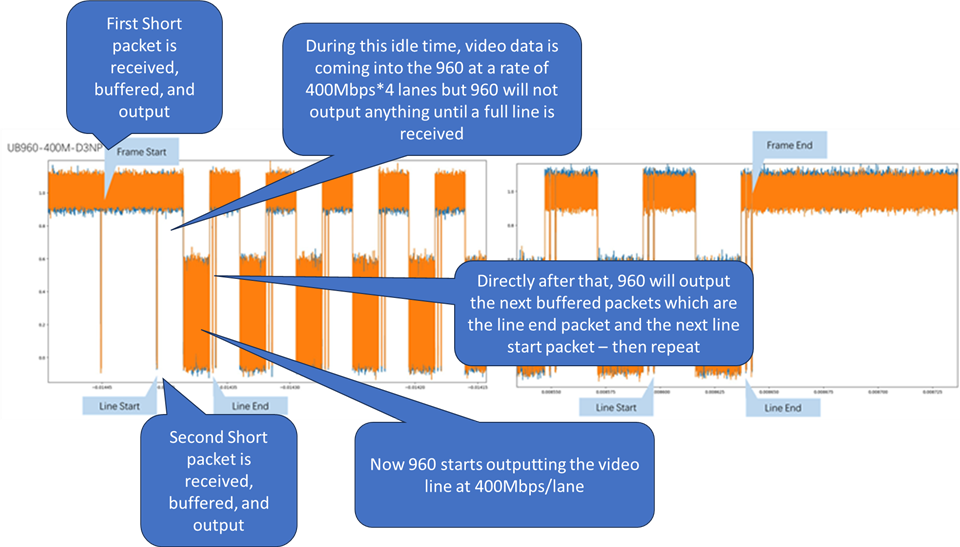

我们探测了传感器和 Orin 之间通道的波形、发现 CSI-2的长和短数据包中的时间规格与 CSI2手册中的要求一致。 然而、与传感器发送的 CSI2波形相比、来自960 CSI2输出端口的帧和线路同步数据包的时序似乎发生了偏移。

帧结束数据包并不出现在帧数据传输的末尾、而是出现在非常接近下一帧开始的地方。 并且线路开始/结束数据包也似乎很奇怪。

在发送线路开始数据包之后、在线路数据之前、始终会保持较长 LP 状态。 但是、线路数据完成后将立即显示线路结束数据包。

传感器 CSI2输出端口波形中的同步数据包正确、但在 DS90UB960输出中使用 SerDes 后同步数据包变得奇怪、这会使我们感到困惑。

我认为在处理串行器/解串器时肯定出了问题、但是根据串行器/解串器中的两个寄存器、我们没有发现任何错误。

您能给我们介绍一下如何解决上述问题吗?

非常感谢、

利