请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1237569/sn65dsi86-sch-check

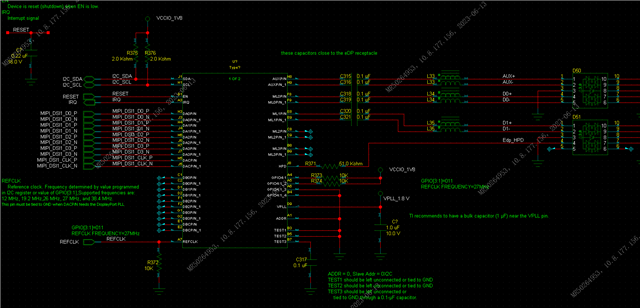

器件型号:SN65DSI86你(们)好。

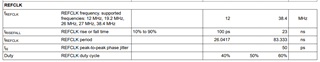

REFCLK 的更多信息、

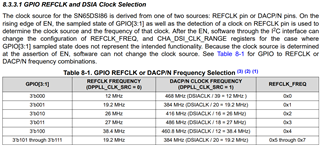

1.该频率由 GPIO[3:1]定义、有12 MHz、19.2 MHz、26 MHz、27 MHz 和38.4 MHz。 可选、如何选择、对应不同频率的屏幕和主控芯片是否有要求?

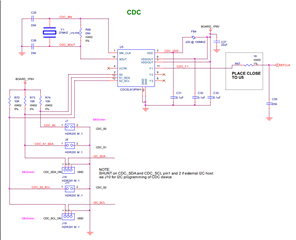

2.此管脚连接到主机控制终端、对主机控制终端引脚有何具体要求? 任何 GPIO 端口都能满足这些要求吗?

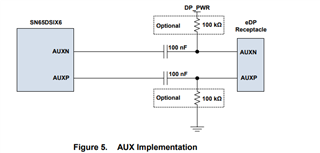

您可以帮助检查 sch 吗? 非常感谢!

谢谢!

雷纳