请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN65LV1023A 您好、,工程师 J ü r

我在使用过程中遇到一些问题、请帮我看看我犯了什么错误。

使用方案如下所示:

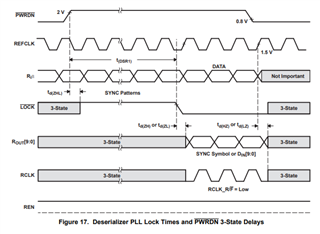

图1显示了1023a 芯片的时序图。

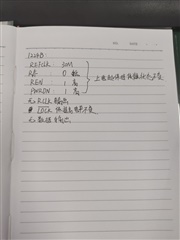

1224b 芯片的配置时钟和引脚电平如图2所示:

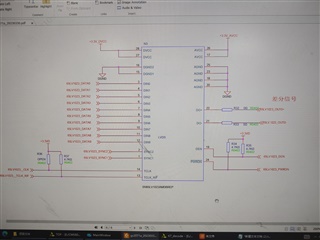

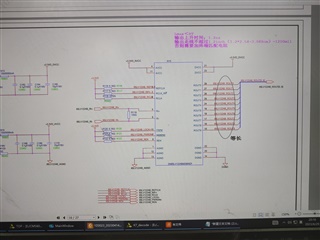

1023a 和 1224b 原理图:

1023a 和 1224b 原理图:

问题如下:

1.芯片初始化操作手册中提到的是否需要将两个芯片的 Pwrdn 引脚拉低一段时间,然后再上拉以完成初始化?

2.回答问题1、需要多长时间才能拉低?

3.连接到问题1。 您是否需要在上电后只执行一次初始化? 或者每个1206输出数据都需要执行初始化操作。

4.我的1224b 没有时钟和数据输出缺少哪一步?

5.请帮忙看看芯片电路是否有问题。