Other Parts Discussed in Thread: XIO2001

大家好、

请告诉我 XIO2001的上电序列。

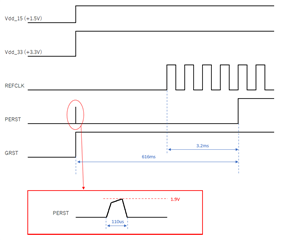

在我们的设计中、Perst#在短时间(1.9V@110us)内转换到 Hi、而+1.5V 和+3.3V 在上升。

波形如下所示。

我们认为很难解决这个问题、但这是否会导致 XIO2001出现故障?

此致、

小林市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.