Other Parts Discussed in Thread: XIO2001

大家好、

请告诉我 XiO 2001的断电顺序。

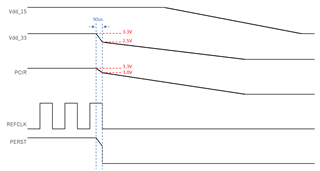

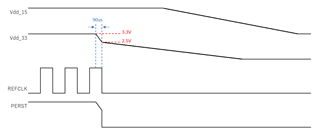

数据表指出、将 PERST #置为有效且停止 REFCLK 后必须移除电源。

但是、在我们的设计中、VDD_33开始下降约90us、速度要快于 Perst #和 REFCLK。

这会损坏 XIO2001吗?

*在下面的线程中,我们认识到在同一时间启用 Perst #和停止 REFCLK 没有问题。

e2e.ti.com/.../xio2001-power-down-sequence-query-modifications

此致、

小林市