在我当前的项目中、有一个信号板、显示以太网 PHY 的 MDI 侧出现异常行为。 其他主板不存在这个问题、它们以100Base-T 全双工模式运行、吞吐量接近100MBit/s。所以这不是一般的设计/布局问题。

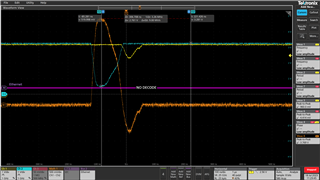

在 RD_P (黄色)和 RD_M (turqouise)测量的图片 I 上的波形。 RJ45连接器中未插入任何器件、因此这是开路测量。 这应该是一个 FLP。

没有正向摆动、并且与其他电路板一样、信号电平变得更接近0V。

您能帮我找出根本原因吗? PHY IC 本身在其引脚上似乎拥有他所需的一切(电压、时钟等)。

AVD 电压为3.3V、IO 电压为1.8V。

如果您需要其他信息、请告诉我。

此致

时间