您好、团队成员:

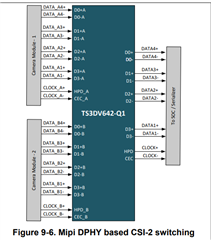

关于 TS3DV642-Q1、我有几个问题。 我们将其用作 MIPI 多路复用器。

1.在一般应用中、显示为 HPD_A 可用于 CLK+。

但是、我们正在将 CEC 用于 CLK+。

请确认是否可以。

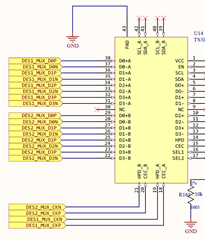

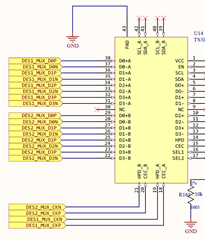

2、目前数据信号和时钟信号都是一个共同切口,因此采用过孔作为时钟信号。 是否建议这样做?

3、差分对的 CLK/D+和 CLK/D-信号之间的最大长度差应该是多少。

4.如果时钟信号功能相同、是否可以通过多路复用器的数据引脚进行路由? 这是为了降低布线复杂性。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、团队成员:

关于 TS3DV642-Q1、我有几个问题。 我们将其用作 MIPI 多路复用器。

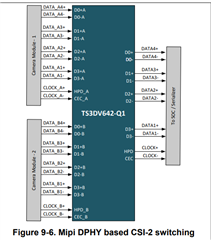

1.在一般应用中、显示为 HPD_A 可用于 CLK+。

但是、我们正在将 CEC 用于 CLK+。

请确认是否可以。

2、目前数据信号和时钟信号都是一个共同切口,因此采用过孔作为时钟信号。 是否建议这样做?

3、差分对的 CLK/D+和 CLK/D-信号之间的最大长度差应该是多少。

4.如果时钟信号功能相同、是否可以通过多路复用器的数据引脚进行路由? 这是为了降低布线复杂性。

您好!

所有数据 I/O 均采用与 TS3DV642-Q1相同的设计、因此、只要输入和输出之间的通道顺序匹配、您就可以通过 CEC 或 DATA 引脚路由时钟信号。

由于 TS3DV642-Q1仅是无源 MUX、最大长度差异将取决于灌电流 RX 可允许或补偿的偏斜程度。 偏斜会来自 PCB 和 MIPI 本身。

由于您使用 TS3DV642-Q1作为 MIPI 多路复用器、您希望支持的最大 MIPI 数据速率是多少? 这是 MIPI-CSI 还是 DSI?

谢谢

大卫