Other Parts Discussed in Thread: DS125DF1610

您好

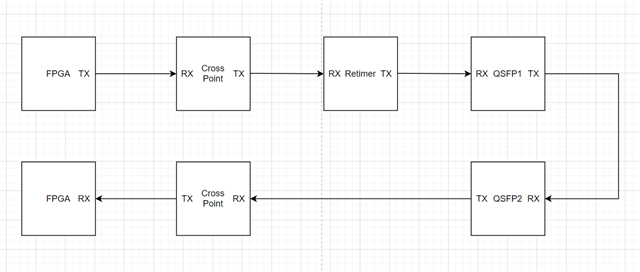

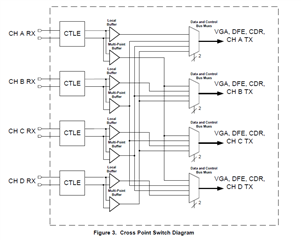

我们的设计中使用了四个 DS125DF1610。 如果我们 在不具有交叉点和电路板播的情况下使用它们、其中一个通道显示 CDR 处于未锁定状态。

输入数据来自其他边界的 FPGA。

我们测试了功率和输入时钟,功率噪声和时钟 的 ppm 可以。

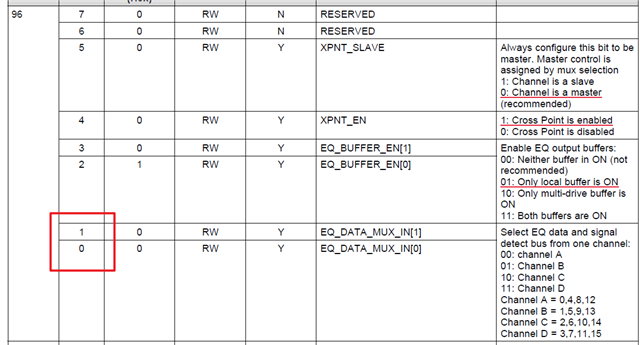

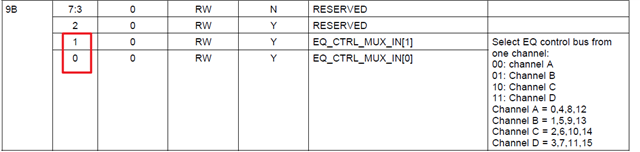

寄存器值如下所示。 regisrer 集是否有任何问题? 为什么 CDR 处于解锁状态?

ds125SharedRegDump 偏差0

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:08 71 20 00 01 08 00 05 00 01 50 00 7a 00 ff

0x10:ff ds125ChannelRegDump dropd 0通道0

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 31 8a 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 00 25 00 02 1c 00

0x90:00 00 00 00 00 14 00 0c 3f 3f 00 D5 99 96 A5

ds125ChannelRegDump 偏离0通道1

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 32 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 68 00 02 1c 00

0x90:00 00 00 00 00 15 00 0c 3f 3f 01 D5 99 96 A5

ds125ChannelRegDump 偏离0通道2

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 2e 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 07 A9 00 02 1c 00

0x90:00 00 00 00 00 16 00 0c 3f 3f 02 D5 99 96 A5

ds125ChannelRegDump 偏离0通道3

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 30 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 00 00 08 00 00 00 00 00 00 00 00 02 1c 00

0x90:00 00 00 00 00 17 00 0c 3f 3f 03 D5 99 96 A5

ds125ChannelRegDump 偏离0通道4

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 31 84 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 00 00 00 00 00 00 00 00 00 00 00 02 1c 00

0x90:00 00 00 00 00 14 00 0c 3f 3f 00 D5 99 96 A5

ds125ChannelRegDump 偏离0通道5

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 34 96 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 07 F5 00 00 02 1c 00

0x90:00 00 00 00 00 15 00 0c 3f 3f 01 D5 99 96 A5

ds125ChannelRegDump 偏离0通道6

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 34 8d 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 00 00 00 00 00 00 00 4F 00 00 02 1c 00

0x90:00 00 00 00 00 16 00 0c 3f 3f 02 D5 99 96 A5

ds125ChannelRegDump 偏离0通道7

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 34 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 07 9e 00 02 1c 00

0x90:00 00 00 00 00 17 00 0c 3f 3f 03 D5 99 96 A5

ds125ChannelRegDump 偏离0通道8

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80 9c 00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 33 8d 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 7e 00 02 1c 00

0x90:00 00 00 00 00 14 00 0c 3f 3f 00 D5 99 96 A5

ds125ChannelRegDump 偏离0通道9

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80 9c 00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 31 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 07 e0 00 02 1c 00

0x90:00 00 00 00 00 15 00 0c 3f 3f 01 D5 99 96 A5

ds125ChannelRegDump 偏离0通道10

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 33 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 01 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 00 00 00 00 00 00 00 3a 00 02 1c 01

0x90:00 00 00 00 00 16 00 0c 3f 3f 02 D5 99 96 A5

ds125ChannelRegDump 偏离0通道11

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 30 84 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 00 00 00 00 02 1c 00

0x90:00 00 00 00 00 17 00 0c 3f 3f 03 D5 99 96 A5

ds125ChannelRegDump 偏离0通道12

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 33 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 13 00 02 1c 00

0x90:00 00 00 00 00 14 00 0c 3f 3f 00 D5 99 96 A5

ds125ChannelRegDump 0通道13

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 35 7e 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 07 ff 00 00 00 00 07 97 00 02 1c 00

0x90:00 00 00 00 00 15 00 0c 3f 3f 01 D5 99 96 A5

ds125ChannelRegDump 偏离0通道14

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 35 84 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8e 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:03 E4 00 00 00 00 00 00 00 00 1f 00 02 1c 00

0x90:00 00 00 00 00 16 00 0c 3f 3f 02 D5 99 96 A5

ds125ChannelRegDump 偏离0通道15

0 1 2 3 4 5 6 7 8 9 a b c d e f

0x00:00 80直流00 01 01 01 60 00 10 6F 08 b4 93 69

0x10:3a 20 e0 90 00 12 7a 36 40 20 a0 03 90 00 E1 55

0x20:00 00 00 40 00 00 00 34 87 40 30 0f f2 00 B6

0x30:00 20 11 88 bf 1f 30 00 10 00 33 8d 35 43 C7

0x40:00 01 04 10 40 08 80 03 0c 30 41 50 c0 60 90

0x50:88 82 a0 46 52 8c b0 C8 57 5d 69 75 D5 99 96 A5

0x60:00 00 00 00 00 00 20 00 0A 22 40 00 00 80

0x70:03 20 00 00 00 22 1a 30 10 00 00 00 48 13 3a

0x80:02 E4 00 00 00 00 00 00 00 00 1c 00 02 1c 00

0x90:00 00 00 00 00 17 00 0c 3f 3f 03 D5 99 96 A5