主题中讨论的其他器件:ALP

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嘿、Sundar、

如果这是 DLP 问题、您需要使用 DLP3030器件名称提交 TT、让 DLP 产品系列在 e2e 上对其进行调查。

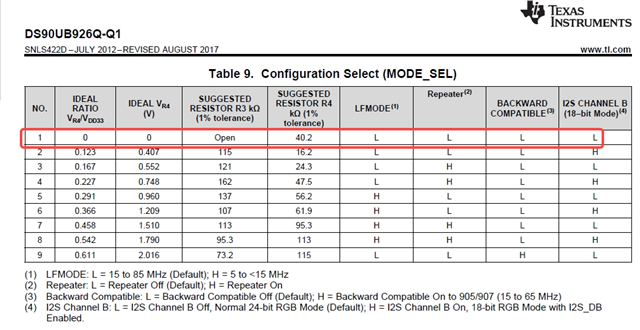

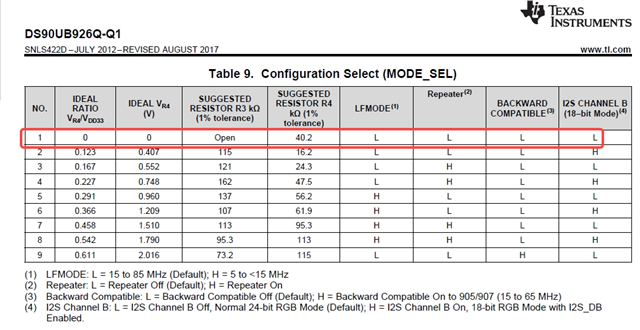

到926、它是相当简单的。 您可以在926上本地运行 ALP 并使用内部时序生成测试图形、以查看是否显示了正确的颜色? 最好测试直接连接显示器的926、以排除数据路径中的 DLP3030问题。

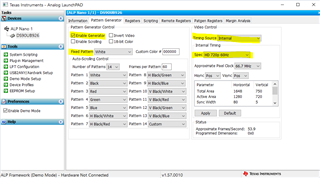

ALP 的初始设置、选择内部时序以排除输入侧的任何内容。 通过这种方法,您可以测试此链接: DS90UB926->DLPC120->DLP3030。

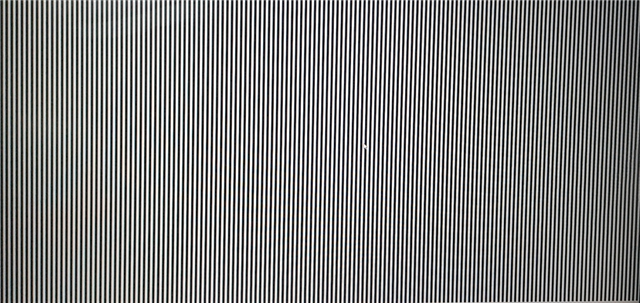

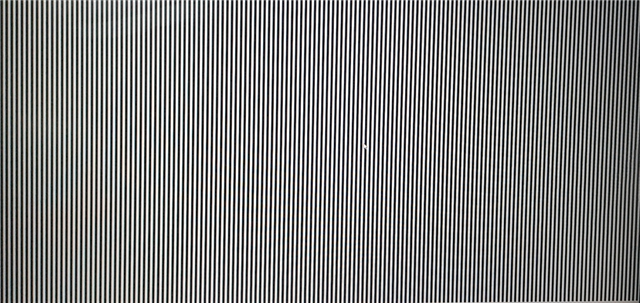

选择您的规格分辨率并选择计时源的内部、然后选择 固定图形(绿色、红色等) 、然后点击"enable patgen"、您应该会在显示屏上看到完全相同的图形。

此致、

Fadi A.

嘿、Sundar、

我们需要完整的时序规格和 PCLK 才能生成脚本。 请参阅960x720 @ 50MHz PCLK 的示例脚本。 您可以 按照此示例脚本对计时参数和 PCLK 进行编程。

此致、

Fadi A.

嘿、 Sundar、

请参阅随附的与您要求的时间有关的内容。 这将从941侧使用内部计时/Clk 运行 patgen。

e2e.ti.com/.../0116.Single_5F00_lane_5F00_941AS.py

此致、

Fadi A.