主题中讨论的其他器件:DP83TC812R-Q1

您好!

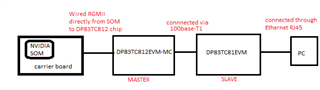

我们使用 DP83TC812R-Q1芯片开发具有100Base-T1接口的电路板。

我们已使用载板检查此情况、如以下连接。

我们已经隔离了 DP83867ERGZR 芯片连接。

检测到链路。 通过 MDIO、MDC 线路通信正常。

但我们无法执行 Ping 操作。

它显示*网络无法访问*

我已在下面附上了此问题的日志。

驱动程序已加载

nVidia@Tegra-ubuntu:~$ sudo dmesg | grep -i eth

[sudo] NVIDIA 的密码:

[ 0.000000] psci:从 DT 探测管道方法。

[4.223949] hns3: Hip08系列的 HiSilicon 以太网网络驱动程序-版本

[4.248077] igb:英特尔千兆以太网网络驱动程序

[4.296360] usbcore:已注册的新接口驱动程序 CDC_ether

[7.424211] OTEE:探测导管方法。

[12.965592] nvethernet 2310000.以太网:添加到 iommu 组51

[12.971985] nvethernet 2310000.Ethernet: failed to read skip Mac reset flag,default 0

[12.980167] nvethernet 2310000.以太网:无法读取 MDIO 地址

[12.986718] nvethernet 2310000.ethernet:无法读取 NVIDA、PAUSE_FRAMES,因此将默认支持设置为 DISABLE

[12.997548] nvethernet 2310000.ethernet: setting to default DMA bit mask

[ 13.004464] nvethernet 2310000.以太网:缺少 NVIDIA,PAD_auto_cal_pu_offset,设置默认值0

[ 13.013583] nvethernet 2310000.ethernet:missing nvidia, pad_auto_cal_pd_offset, setting default 0

[ 13.039802] nvethernet 2310000.以太网:以太网 MAC 地址:48:b0:2d:94:41:3d

[ 13.047748] nvethernet 2310000.以太网:DT 中的 MACsec param 缺失或禁用

[ 13.055538] nvethernet 2310000.以太网:DT 中不支持/未启用 MACsec

[ 13.065800] nvethernet 2310000.以太网: eth0 (HW ver: 53)创建了8个 DMA 通道

[ 18.883875] TI DP83TC812CS2.0 2310000.以太网:00:~~~~~~~~~~~ 已加载~~~~~~~~~~~

[ 18.884279] MDIO_BUS 2310000.以太网:~~~~~~~~~~ 在地址0处打印 phy

[ 19.100012] TI DP83TC812CS2.0 2310000.以太网:00:~~~~~~~~~~~ 已加载~~~~~~~~~~~

[63.126826] IPv6:ADDRCONF (NETDEV_CHANGE):ETH0:链路就绪

[63.127398]以太网2310000.以太网 eth0:链路已接通- 100Mbps/全-流控已关闭

驱动器自举寄存器

NVIDIA@Tegra-ubuntu:~$ sudo dmesg | grep -i dp83

[ 18.670154] dp83812_read_strap 配置:strap 配置为0x4280

[ 18.883875] TI DP83TC812CS2.0 2310000.以太网:00:~~~~~~~~~~~ 已加载~~~~~~~~~~~

[ 18.884494] dp83812_read_brands:strap 配置为0x4280

[ 19.100012] TI DP83TC812CS2.0 2310000.以太网:00:~~~~~~~~~~~ 已加载~~~~~~~~~~~

未分配 IP

NVidia@Tegra-ubuntu:~$ ifconfig

ETH0:flags=4163 MTU 1500

inet6 fe80::ae9f:68c9:9e64:82d prefixlen 64 scopeid 0x20

乙醚48:b0:2D:94:41:3D txqueuelen 1000 (以太网)

RX 数据包0字节0 (0.0B)

RX 错误0丢弃0溢出0帧0

TX 数据包73字节12523 (12.5KB)

TX 错误0丢弃0溢出0载波0冲突0

LO:flags=73 MTU 65536

iNet 127.0.0.1网络掩码255.0.0.0

inet6 :: 1 prefixlen 128 scopeid 0x10

循环 txqueuelen 1000 (本地回送)

RX 数据包1110字节71114 (71.1 KB)

RX 错误0丢弃0溢出0帧0

TX 数据包1110字节71114 (71.1 KB)

TX 错误0丢弃0溢出0载波0冲突0

错误消息

NVIDIA@Tegra-ubuntu:~$[ 264.950727] nvethernet 2310000.Ethernet: Failed to report error:Reporter ID:0x0、Error code:0x1001、return:-19

已使用静态和动态 IP 配置尝试 Ping。

NVIDIA@ó n Tegra-ubuntu:~$ ping 8.8.8.8

Ping:连接:无法访问网络

nVidia@Tegra-ubuntu:~$ sudo ethtool eth0

[sudo] NVIDIA 的密码:

ETH0的设置:

支持的端口:[ TP MII ]

支持的链接模式:未报告

支持的暂停帧使用:对称仅接收

支持自动协商:否

支持的 FEC 模式:未报告

通告的链路模式:未报告

广播的暂停帧使用:否

广播的自动协商:否

广播的 FEC 模式:未报告

速度:100Mb/s

双工:全双工

端口:双绞线

PHYAD:0

收发器:内部

自动协商:关闭

MDI-X:未知

支持唤醒:D

唤醒:D

当前报文级别:0x00000000 (0)

检测到链路:是