Other Parts Discussed in Thread: TCA9517

主题中讨论的其他器件:TCA9517

大家好、

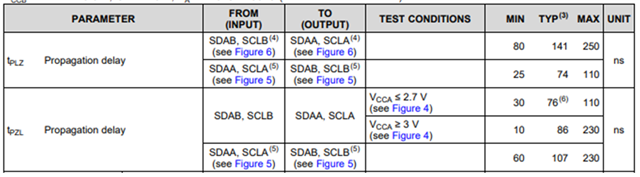

数据表显示了 A 到 B 或 B 到 A 的延迟时间、但如果输入期间 SDAA 和 SCLA 之间的间隔为5ns、则输出端 SDAB 和 SCLB 之间的间隔也可以保持在5ns 吗?

谢谢

利利连

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Lillian:

感谢大家学习与此相关的背景知识。

您可以看到下面的波形

这是使用2个独立板(顶部波形为板1、底部波形板2)吗?或者您是否使用了1个板但替换了 TCA9517? 其中一部分还可能与 CPU 生成信号以及具有不同偏差有关。 在使用两个不同的电路板时、很难判断9517或 CPU 是否产生了最大偏差。

但另一个产品是4.9ns,那么 SCL 和 SDA 之间的通道偏移是否可由芯片或随机控制?

我们不测试通道之间的偏斜时间、因为这通常对 I2C 无关紧要(下面的说明)。

数据保持时间是 I2C 总线的系统级规格。 从 I2C 器件状态机的角度来看、数据保持时间不应导致数据采样出现问题或缺少 ACK、因为数据应在上升时钟边沿而不是下降时钟边沿进行采样 (在我看来,数据设置时间是一个更重要的参数,在这个原因比数据保持时间)。 如果器件发生故障或因此获取了不正确的数据、则意味着器件本身会尝试在下降时钟沿对数据进行采样、这意味着在数据转换和准备采样的时间内提供的裕度非常小。

----------------

权变措施:

从系统级别、您可以通过更改 数据信号上的 RC 常数来帮助提供更大的裕度。 由于保持时间的时序是基于下降沿的、因此 RC 常数中的 R 是 生成 数据信号的器件的下拉 FET。 您可以在生成时钟信号的器件前面放置一个串联电阻以使 R 更大、从而减慢下降时间、或者您可以增加数据线上的电容以使 RC 更大(不过也会影响上升时间)。 您也可以同时执行这两种操作。

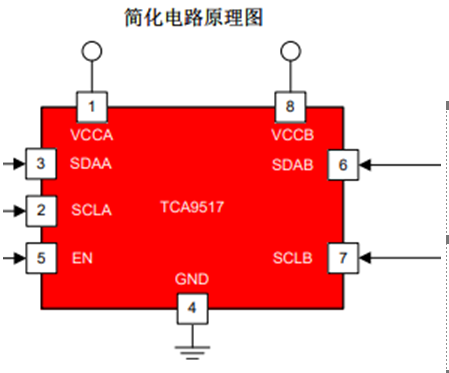

或者、您也可以使用另一个 TCA9517、在这里、您可将 SDA 线路通过 SDAB 路由到 SDAA、再将 SCLA 路由到 SCLB、并且让时钟信号不通过缓冲器。 这将强制 SDA 信号通过 TCA9517的2倍传播延迟、并且 SCL 信号将具有更多的设置时间裕度。

-鲍比