https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1277634/ds160pt801-ds160pt801

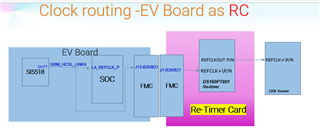

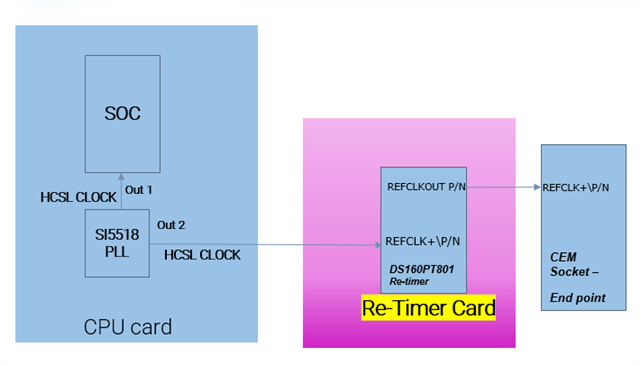

器件型号:DS160PT801在下面的电路板 FYR 中粘贴了建议的时钟布线。

此问题与 DS160PT801有关。 我们 的电路板中有 SI5518、想要将 HCSL 时钟从 Si5518连接 到 DS160PT801 RFCLK 输入。下面是个问题

1. 从 SI5518到 DS160PT801的时钟传播延迟(PCB)是否会影响性能?

如果是、我们是否可以 在 DS160PT801中调优/调整此延迟?

谢谢

Prashanth PAI B