大家好、

我们是否有关于此差分线路接收器在温度、负载和工艺变化范围内的传播延迟的任何数据或见解?

我的客户正在尝试获得可重复的传播延迟、因此非常感谢您在此提出任何见解。 如果它们能够在不同器件之间具有更多可重复的传播延迟、则它们将接受采用相同尺寸的替代建议。

谢谢。

日文

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们是否有关于此差分线路接收器在温度、负载和工艺变化范围内的传播延迟的任何数据或见解?

我的客户正在尝试获得可重复的传播延迟、因此非常感谢您在此提出任何见解。 如果它们能够在不同器件之间具有更多可重复的传播延迟、则它们将接受采用相同尺寸的替代建议。

谢谢。

日文

尊敬的 JP:

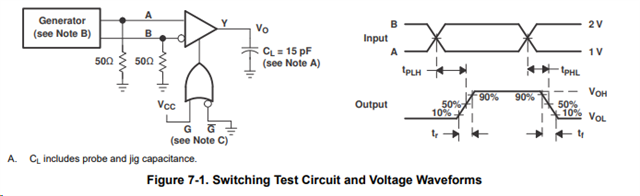

因此、该器件在 tPHL 和 tPLH 两种情况下的传播延迟均为最小值8ns;典型值16ns;最大值26ns、测试设置如下:

负载为15pF。

我们不会在其他负载将数据接收为传播延迟、因此数据的负载是恒定的。 话虽如此、更多的输出电容将减少传播延迟。 我们的测试设置尝试尽可能减少负载对传播延迟的影响、因此我们将测量器件性能、而不是关注负载的 RC 充电常数。 由于它测量的是50%至50%点-输出的上升时间由负载电容和输出电阻决定。 在我们的测试设置中、我们将容性负载降至最低、以便我们可以测量器件性能。 但是、如果您增加电容负载、则充电时间从0%到50%会随着电容的增加而按比例增加 -即、如果输出负载翻倍、则上升时间会增加一倍-这将随着充电时间增加到50%而增加传播延迟。

一般来说、温度较高也会减慢器件的速度、因为输出阻抗会随温度的升高而增加。

至于可预测的传播延迟-如果负载电容为15pF 或更低、则将处于指定的8ns 至26ns 范围内(通常而言- 50%充电时间应约为1.5ns -因此相当小-但输出阻抗会显著改变它) -我真的不认为我会给你更好的时间-因为在所有现实情况下,当我进行近似输出阻抗-在这个设备上它从20欧姆到1k 欧姆取决于使用情况 (在最低 VCC 和最高温度以及低输出电流(-100uA)情况下存在最高值)。

就传播延迟变异性而言、没有比这更好的器件了- HL 和 LH 转换间的偏差最大为6ns (输出电容越大、误差可能越长) 因此虽然此器件上的覆盖范围较大、但不会出现很多与之相关的偏差。 一般而言、我们会尝试告诉客户、只要系统内的最大传播延迟和脉冲最大脉冲偏斜是可以接受的、它的可变性应该不是大问题。 但是、输出电容越低、通常也会得到更好的结果。

这可能没有他们正在寻找的帮助-但我们没有太多数据来支持请求。 本质上、更高的温度和更低的 VCC 将增加传播延迟、而更高的 VCC 和更低的温度将减少传播延迟、因为硅在较低的温度下电阻较小、而在较高的温度下电阻较大。

如果有任何其他问题、敬请告知!

此致!

帕克·道德森