Other Parts Discussed in Thread: DP83825EVM

主题中讨论的其他器件:DP83825EVM

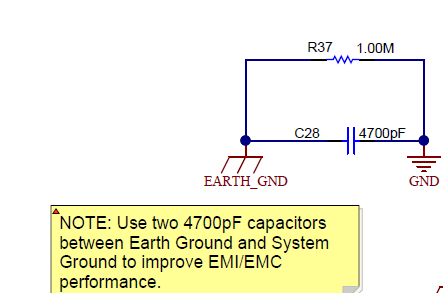

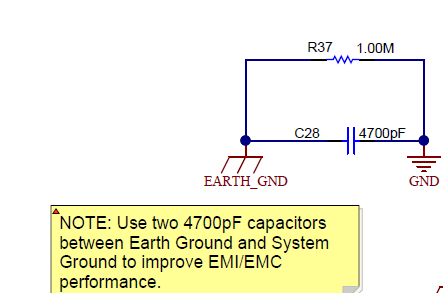

- 在 DP83825IRMQR 的 EVK 中、建议使用2个4700pf 电容器。 无法理解使用1M 电容器的单个4700pf 本身会对 EMI 有所帮助。 为什么推荐2个?

- 同时也说明了该网络如何帮助改善 EMI。

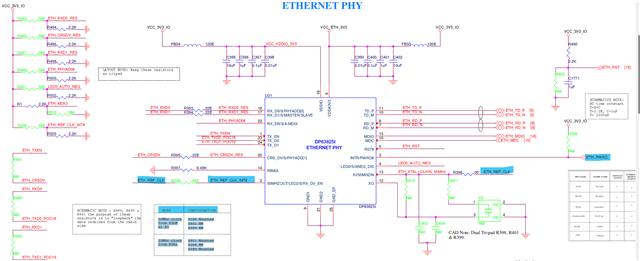

- 共享 EVK BOM。

- 在下方附加图像

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: DP83825EVM

尊敬的 SM Kalim:

所示的接地电路为任何 EMI 噪声提供了更好的返回路径。

我们知道需要更新 DP83825EVM 的用户指南、新版本将包含 BOM。 不过、EVM 的设计文件位于产品页面上、我可以根据这些文件生成 BOM。 请查看附件。

e2e.ti.com/.../HSDC045A_2800_001_29005F00_BOM.xls

此致、

阿尔瓦罗

谢谢您的支持、Alvaro。

请查看以下问题:

应用处理器

您好、Kalim:

我已经查看了您的问题、并在下面对它们做出了回答。 如果我漏掉了任何内容、请告诉我。

您能指导我有关 pin3 (INTR/PWRD#)吗? 我可以将此引脚连接到 AP 的 GPIO 并提供上拉作为 NM 吗?

是的、如果 安装了 R396、则可以按预期工作。

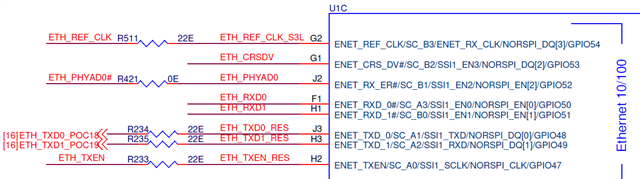

我要将 PHY 设置为在从模式下工作,因此 PIN2 (50MHZOUT/LED2/S/RX_DV_EN)不会连接到 AP 的输入;它将悬空。 此外、我会将 AP 的引脚(50MHz O/P)连接到 PHY 的 XI 引脚、因为 AP 的 G2引脚(ENET_REF_CLK)仅为输出。

此外、我在实施 RMII 时查看了应用手册、 并且规定 PHY 的50MHz 管脚应连接到 AP 的输入端。 但在本例中、这种情况是不可能的。 您能否指导我、如果50MHz 引脚未连接到 AP、PHY 的行为是怎样的?

AP 正在向 PHY 的 XI 引脚提供50 MHz 时钟信号,这是可以 的。 我理解您的困惑、因此我想重申、PHY 可以使用 AP 提供的50 MHz 时钟。 在 RMII 从模式下、MAC 和 PHY 需要共享相同的时钟、但 数据表的第7.3.10节"简化媒体独立接口"隐藏一句话、表示 AP 可以为 PHY 提供时钟。

此致、

阿尔瓦罗

您好、Kalim:

负载电阻器和电容器因晶体的供应商型号而异。 数据表的第8.2.1.1.2节 对其进行了提及、并提供了指向另一份包含更详细信息的文档的链接。

至于图像复审、

我建议包括:

其他一切看起来都很好。

此致、

阿尔瓦罗

尊敬的 Alvaro:

感谢您的反馈!

请针对以下问题提供您的输入:

晶振器件型号- CS32-F1010FM08-25.000M-TR

负载电容器-18PF

你好,Kalim!

本节讲述了晶体的最大功率输出、以及如何避免超过该最大值(例如、如果最大驱动输出为100uW、不能始终持续消耗150uW、则会降低晶体性能)。 低至100uW 的驱动电平就是最低要求的一个例子。 如果您选择的晶体是300uW、那更好! 我查看了您提供的数据表、发现该晶体符合 DP83825数据表的表112中列出的规格。

至于 RS 值、360应该可以、但我想重申、对于晶体供应商来说、这是一个更好的问题。

此致、

阿尔瓦罗