Other Parts Discussed in Thread: DP83825EVM, USB-2-MDIO

主题中讨论的其他器件: USB-2-MDIO、 DP83825

我正在尝试使用一对 DP83825EVM 板向 FPGA 评估板添加两个10baseT 接口。 我已经在将 RMII 连接到 J9的焊盘中添加了零欧姆电阻、并将 J9连接到合适的 FPGA 板端口、同时将 FPGA 编程为基本的 MAC。 我在 R46上添加了一个零欧姆电阻器、移除了 R41、并通过具有100欧姆阻抗的双绞线将50MHz 时钟从 FPGA 板连接到 J14。 我已移除 R53和 R54以及将有线 FPGA IO 连接到 J10、以支持从 FPGA 进行寄存器读/写。 我已经为 CLKOUT 添加了一个2.49K 上拉电阻器以分配 RXDV 引脚功能。 我已经在 R45上添加了一个零欧姆电阻器来设置受控模式。

为了进行初始测试、我在 RMII RX 端口上提供了一个10Mbps 数据包发生器、并且正在运行近端回送测试。 为此、我写入了以下寄存器:

寄存器0x0000:0x0100

寄存器0x0017:0x0081

寄存器0x0016:0x0001、0x0002、0x0004、用于各种近端环回功能。

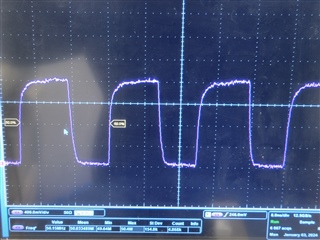

将测试数据包应用到 RMII RX 端口、我看到返回的 RMII TX 信号如下所示:

0x0001:信号

0x0002:无信号

0x0004:无信号

因此我显然在 PCS 输出端和后续的回送丢失。 我可能做错了什么?