请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

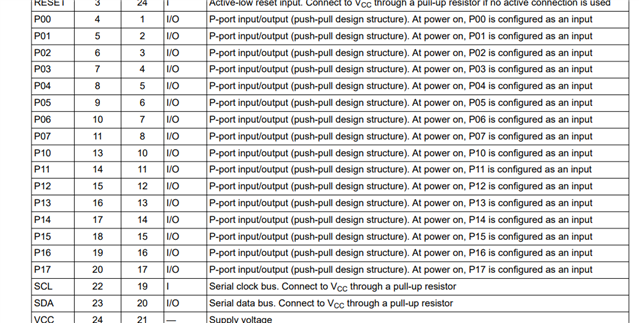

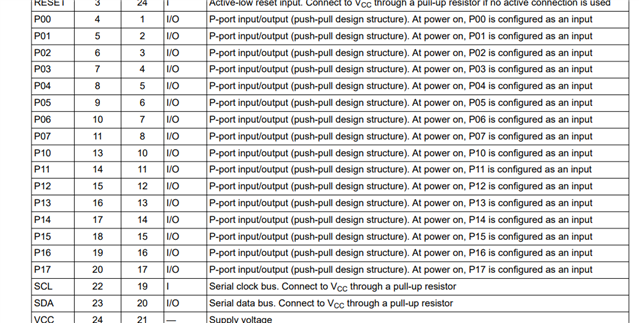

器件型号:TCAL9539 客户希望将 GPIO 配置为开漏。

但我认为它是推挽式设计结构。

那么、它是否可用呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

客户希望将 GPIO 配置为开漏。

但我认为它是推挽式设计结构。

那么、它是否可用呢?

尊敬的 Fabio:

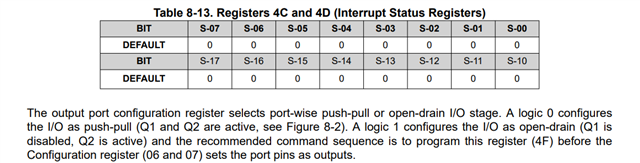

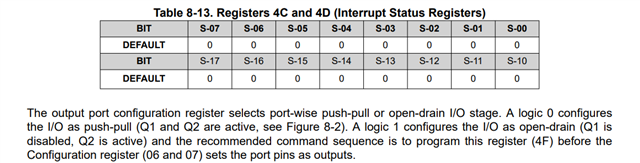

遗憾的是、这是基于端口的、这意味着除非配置了整个端口、否则无法通过推挽/开漏方式单独控制 p 端口。

与此相关的方法有不同。 请参阅 此处的常见问题解答、了解如何通过输出和配置寄存器进行开漏输出及其影响。

此致、

泰勒