您好!

我们拥有从1.8V RGB888转换至3.3V LVDS 显示屏以及从 RGB 转换至 DVI/HDMI 的设计。

在某些产品中、TFP410将不是必需的且没有爆裂声。

- 是否建议在未组装时如何处理布局中的残桩?

- 残桩是否应以某种方式端接?

非常感谢、Keith

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、谢谢! 我们还有几个 Quesitons:

使用 TFP410 I2C/RST 低电平的手动配置时、是否可以将设计配置为在未连接监视器时禁用 T.M.D.S 发送器并在连接监视器时重新启用?

示例:

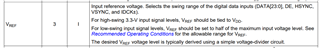

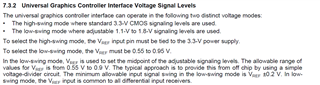

此外、通过配置 VREF 上的电压电平、可以将 TFP410配置为使用不同的 CMOS 输入标准(1.1V 至1.8V)。 如果使用1.8V CMOS 标准、VREF 应配置为½ 1.8V、即0.9V。

非常感谢 Keith

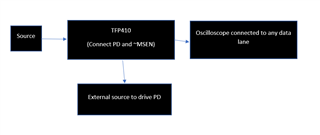

要了解您是否可以使用热插拔来断电/打开器件、最好使用如下方框图所示的测试设置。

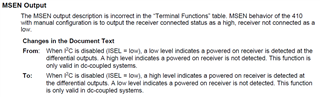

请记住、当检测到监护仪时、MSEN 被拉至低电平;当未检测到监护仪时、MSEN 被拉至高电平。 这意味着您需要反转 PD 和 MSEN 之间的信号、因为当 PD 为低电平时、器件将处于断电模式。 如果在 MSEN 为低电平时在示波器上看到信号、则可以使用适当的显示继续测试。

Vref 将设置以下引脚的电压摆幅:

我建议不要超过建议的最大0.9V。 您是否可以降低由 Vref 设置的引脚的电压摆幅、或仅使用完整的3.3V 电压?

尊敬的 Vishesh:

MSEN 在勘误文档 SLLZ030A–2003年6月–2009年4月修订、下面进行了更正:正确吗?

该数据表显示 TFP410支持接口标准:1.1至1.8和3.3 CMOS 输入电平。 CMOS 输入是通过 VREF 引脚配置的。 使用 TFP410的主板上的 SLLA152 - 2003年9月 DVI 表明使用了1k 电阻器来配置低摆幅。 数据表还引用了低摆幅模式、并在文本中指明了 VREF 必须为0.55V 至0.95V、然后在数据表的同一节中指明了0.55V 至0.90范围。 对于1.8V 标准、0.95是正确的。 对1.8V 逻辑电平配置有何建议?

非常感谢您的输入、 Jim