主题中讨论的其他器件:AM6442、 DP83869

大家好!

我在 一周前问这个问题,但现在才意识到我不理解被接受的答案。

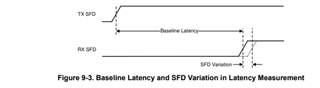

我们希望 将 DP86839的 GPIO_0和 GPIO_1引脚用于 TX 和 RX SFD 的1588硬件时间戳。 为此、我们将使用0x1E0[3:0]= 0x6 =接收 SFD 来配置 GPIO_0、使用0x1E0[7:4]= 0x5 =发送 SFD 来配置 GPIO_1。 我们的时间戳器件(AM6442 CPTS) 需要最小98ns 的脉冲宽度。

问题1: GPIO_0和 GPIO_1上的 SFD 脉冲是否可以延长以确保其宽度大于98ns?

问题2. 在之前链接的答案中、我被告知使用0x1E0[7:4]以8ns 的增量调整 SFD 脉冲时序。 但数据表显示0x1E0[7:4]适用于 GPIO_1_CTRL。 这是不是错了? GPIO_0和_1上是否有另一个寄存器来调整 TX/RX SFD 的脉冲时序?