Other Parts Discussed in Thread: DP83867CR

主题中讨论的其他器件:DP83867CR

您好!

这是相关问题的延续。 下面是我当前希望实现的目标的摘要。

・通过 WoL 启动 CPU。

・在使用 WoL 启动 CPU 之前、PHY 电源已打开、但 CPU 电源已关闭。

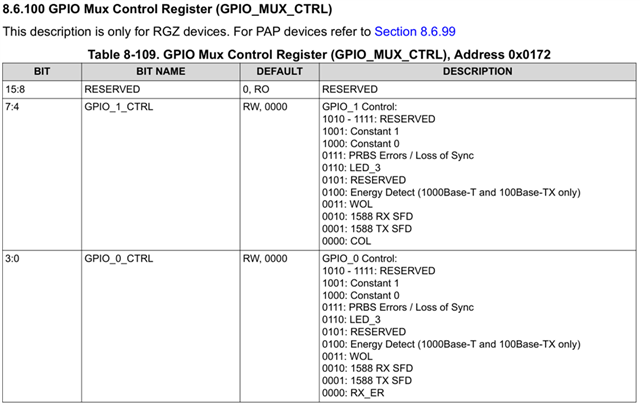

・将 PHY 的 GPIO 连接到 WoL 与为 CPU 供电的电源 IC 的使能引脚、并首先启动电源 IC。

・1 μ s 后、CPU 开启并启动通信。

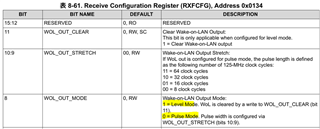

通常、WoL 是使用 CPU 的 GPIO 中断启动的、但上述方法有些不规则、因为 WoL 是在 CPU 断电的情况下执行的。 从相关的问题中可以看到、人们对 WoL 的 GPIO 是脉冲输出、因此有必要在 GPIO (PHY)-使能(Power IC)中配置锁存电路。 但是、通过查看 DP83867CR 数据表、可以看出、如果设置了 WOL_OUT_MODE ="1"、则不需要锁存电路。 是否不需要锁存电路来使用上述配置来实施 WoL?

谢谢。

科诺