您好、Mellin

我继续在此处通过电子邮件提出问题。

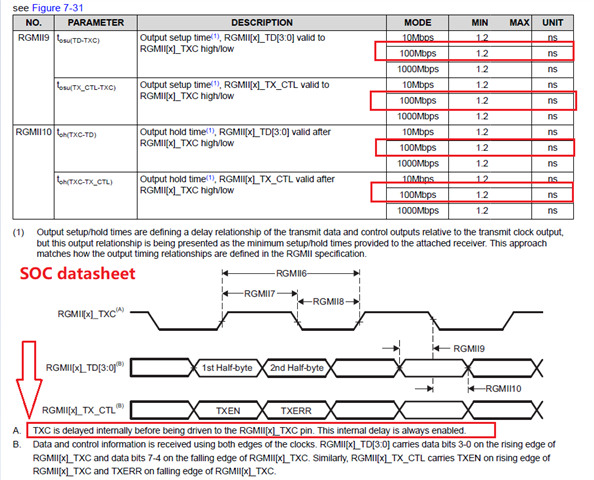

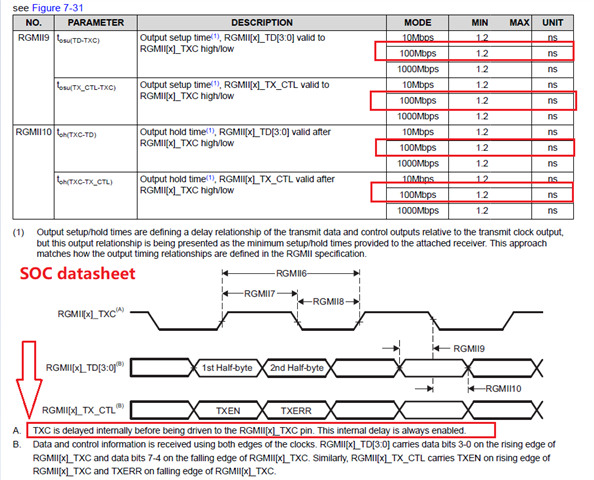

100Mbase-T1 RGMII 在移位模式下运行、与 SOC 通信。

在电子邮件中、您的回复如下:

1.关于 RGMII 输出时序:

RX 时序参数在 RGMII RX 接口的输出引脚上指定、对吗?

参数需要匹配接收器的(SOC)输入规格、对吗?

RGMII TX 和 RX 对齐模式或延迟(移位)模式配置

在上面的快照回复中、对于下面的配置、您已确认我的理解正常:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Mellin

我继续在此处通过电子邮件提出问题。

100Mbase-T1 RGMII 在移位模式下运行、与 SOC 通信。

在电子邮件中、您的回复如下:

1.关于 RGMII 输出时序:

RX 时序参数在 RGMII RX 接口的输出引脚上指定、对吗?

参数需要匹配接收器的(SOC)输入规格、对吗?

RGMII TX 和 RX 对齐模式或延迟(移位)模式配置

在上面的快照回复中、对于下面的配置、您已确认我的理解正常:

Yanan、您好!

请在下面查找我的评论:

RX 时序参数在 RGMII RX 接口的输出引脚上指定、对吗? 参数需要匹配接收器的(SOC)输入规格、对吗?

正确。

谢谢。

大卫

谢谢、David。

正如我在下面所理解的、它们都对吗?

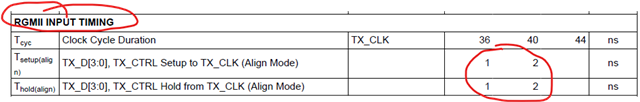

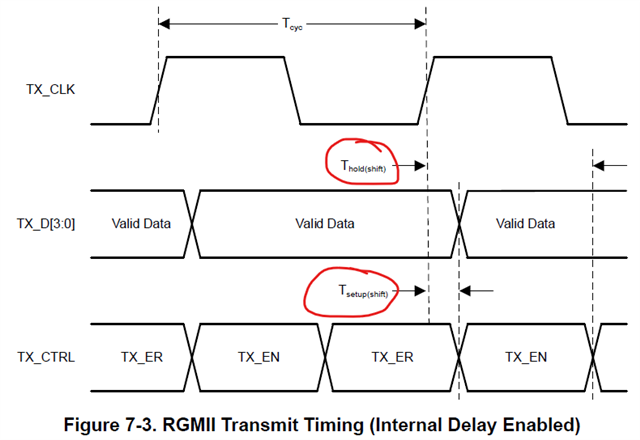

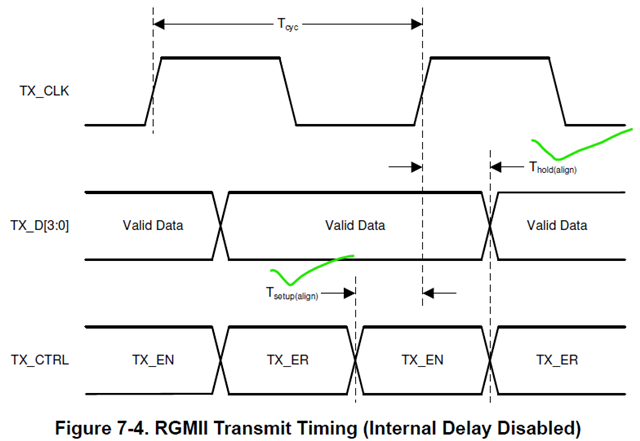

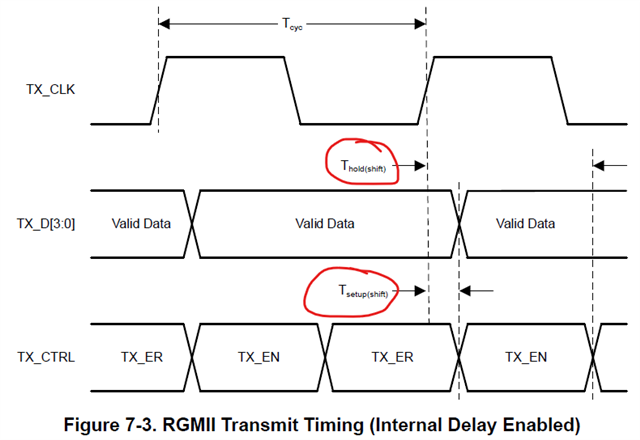

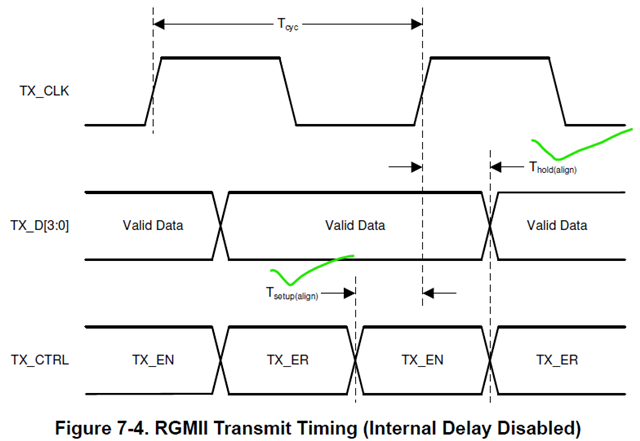

1.关于 RGMII RX 或 TX、不管接收到时钟和数据是否同步、 移位模式都会引入 PHY 内的时钟延迟、对齐模式会使原始信号时序保持不变、而不会引入其他延迟。

2.对于接收器,无论 PHY 还是 MAC,接收到的数据都必须在接收器内部的时钟边沿上采样。

3.如果 PCB 上 RGMII 总线的所有轨道的并行长度相同、时钟和数据的转换时间相同、则 PCB 轨道不会造成转换延迟。 但对于接收器、数据必须在时钟边沿到达之前保持稳定、因此延迟是在接收器内部引入的。

(对齐模式下的发射极) + (PCB 轨迹的长度相同)=(数据和时钟在接收器侧同步)=>接收器必须进入移位模式;

(移位 模式下的光发射极) + (PCB 轨道长度相同) = (时钟 在接收器侧传输数据后延迟) => 接收器必须进入对齐模式。

如果 PCB 引线的长度不同、这会在数据和时钟信号之间产生转换延迟、则可以根据转换延迟选择移位模式或对齐模式、以匹配接收器的接收时序。

无论什么情况、目标都是使接收时序正常:数据必须在时钟边沿之前保持稳定、其中接收数据的 t_setup 和 t_hold 与接收器的数据表兼容。

您好、David。 感谢您的回复和赞扬。

现在就可以清楚对齐/移位模式和时序了。

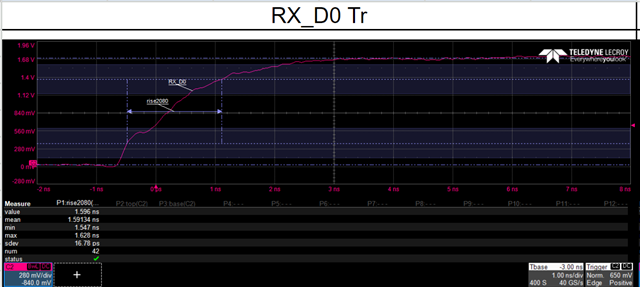

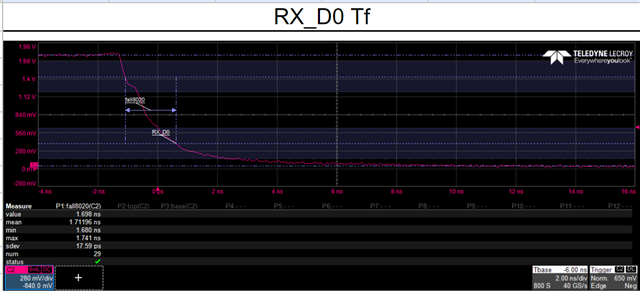

根据我们的测试结果、 数据上升/下降时间不兼容 测量最大电压。

测试中的 tr 和 tf 1.59ns 和1.71ns、 但数据表中指定了 1.2ns 最大值 具有5pF Cload。

我正在考虑:RX_D[3:0] tr 和 tf 的超范围可能为 接受或不接受 如果接收器 SOC 的接收时序良好( SOC 的数据表中指定 t_setup 和 t_hold 大于1ns)?