请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

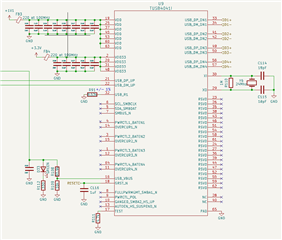

器件型号:TUSB4041I 我正在设计一个板、它包含四个 IC (FT4232H 四路高速 USB 到通用 UART/MPSSE IC)、可以将四个串行 RS -232信号转换为一个 USB 差分信号、所有 IC 都按照 USB2.0标准协议运行。 我希望使用 TUSB4041I 四端口 USB 2.0集线器、将这四个 USB 信号合并到单个上行 USB A 连接器中。 此电路板将使用5V 进行自供电。 鉴于下游端口不会消耗功率、对于如何设置集线器以使其符合此设计、我有一些问题:因为下游唯一的连接用于 D+/D-、我假设给定端口不存在这样的情况: 出现过流。 鉴于此、我不实现电源开关并将所有 PWR 引脚保持未连接状态。

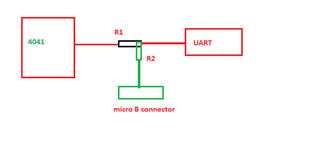

- 传统上、我使用直接 USB 迷你连接器通过 UART 对每个下行端口上的 EEPROM 进行编程、从而将其连接到 USB IC。 我必须执行此操作来为每个 IC 设置 VID 和 PID、以便它们能够被识别为不同的实体。 我是能够通过此集线器 IC 单独写入这些 EEPROM、还是应该沿着下游 USB 信号实施 USB 迷你连接器以便与每个串行转换器及其 EEPROM 直接连接。 此外、如果是后者、这是否会引入会削弱下行端口上信号的噪声?

- TUSB2046 IC 等其他 TI USB 集线器讨论了如何在 USB 差分信号对上实现瞬态抑制器和降噪电路;但未提及此 IC。 是否有用于 ESD 保护和信号完整性的内部组件? 如果不是、为了在外部实现这一点、我应该遵循哪些指导原则?

- 我担心 RESET 信号的条件。 我使用与该集线器 IC 评估板相同的3.3V 和1.1V 稳压器、该评估板的1.1V 稳压器具有200 us 的延迟。 根据数据表第7.6节中的时序表和图表、我需要主动复位; 但是、评估板通过一个0.1uF 的电容器将 GRSTZ 接地、就像集线器被设置为被动复位一样、该复位假定 VDD 必须在 VDD 3.3之前稳定、这与刚才假设的相反。 实施是否正确?