Other Parts Discussed in Thread: TCA9801, TCA9803, TCA9509

主题中讨论的其他器件:TCA9803、TCA9801 、

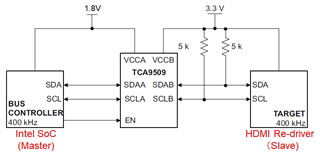

大家好、TCA9505支持团队

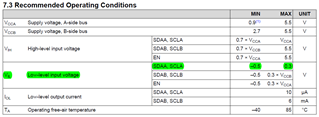

以下是从数据表中获取的建议工作条件和电气特性。

在建议运行条件中描述了 VIL 低于0.3V。 然而、在电气特性中规定 VILC 最小值为110mV。

这项建议似乎不一致。 我认为建议的 VIL 应小于110mV。 为什么建议使用0.3V?

我已阅读过其他 E2E 文档、但不明白这一点。

此致、

田尾市