主题中讨论的其他器件:DS160PR810、 DS320PR1601、 DS320PR410、DS160PR410 、DS160PR1601

1.在本参考设计中、只有 PCIe 的数据信号已被转驱动、而 PCIe 的 clk 信号尚未经过转驱动。 REFCLK 的衰减是否相对低于数据信号的衰减、以便即使未像参考设计中那样进行处理、也可以正常使用 REFCLK? 此外、是否可以像数据信号那样使用转接驱动卡来增强 REFCLK?

2.单个 DS160PR810能否同时处理双端口 X4宽度 PCIe 链路、从而有效利用全部8个 LAN?

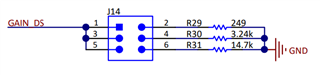

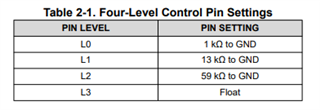

在参考设计中、为什么 J14的接地电阻与表2-1中所述的接地电阻不同?