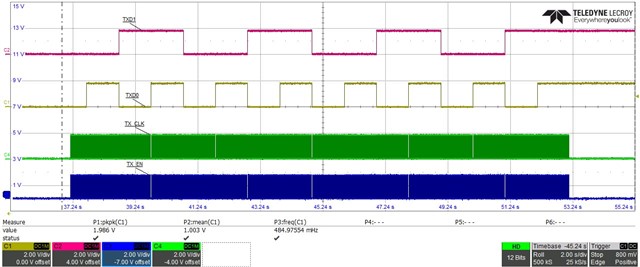

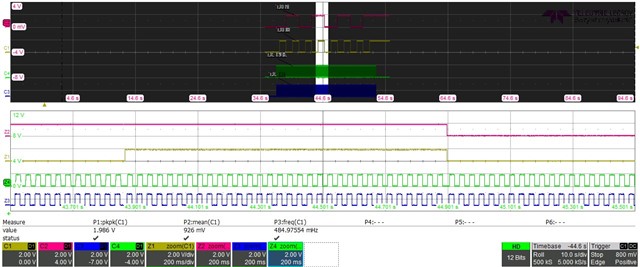

我目前正在尝试对 PHY 进行一些功能测试、以验证 RGMII 与 FPGA 的连接。 我使用 JTAG 边界扫描单元来读取和写入信号。 我使用边界扫描而不是对 FPGA 本身进行编程、因为我们想要在生产验证中使用 JTAG、而无需对 FPGA 进行编程。 这意味着我以非常低的频率运行、TX_CLK 以大约33Hz 的频率运行。 这里可能有一些问题、但我们从用于其他 PHY 的 JTAG 获得的示例项目使用相同频率且没有任何问题、因此我假定这些信号对本应用是正确的、但仍然有确凿的证据。 不会显示 Rx 线路、但不显示任何活动。

由于我根本无法在 RX 线路上获取任何内容、 这使我认为我尚未正确配置寄存器以使其进入 MII 环回模式。 根据数据表、我采用了以下配置:

寄存器 名称 值

0xFE LOOCR 0xE720 (由数据表指定、但未进一步指明此寄存器的设置)

0x0 BMCR (BMCR) 0x4100 (启用 MII_Loopback、重新协商关闭以及仍为全双工)

0x16 BIST 0x4 (在使用和不设置该寄存器的情况下尝试、数据表意味着只有在100Base-TX 模式中才需要、但无论如何也会尝试)

我已经读回这些寄存器、因此我确信它们的设置方式与我在这里提到的相同。 是否有什么明显的东西让我失踪了?