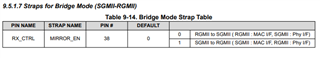

主题中讨论的其他器件: DP83869

您好!

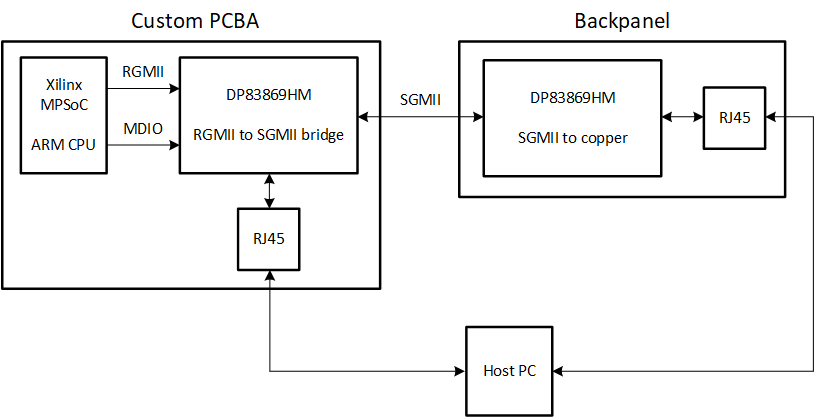

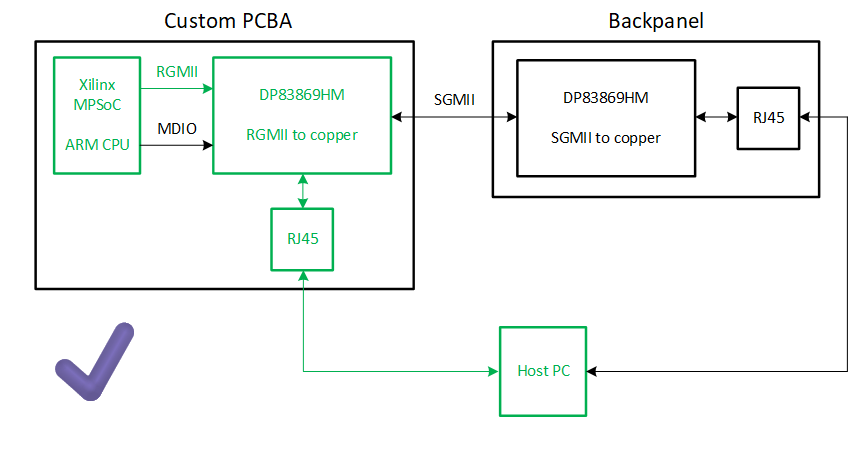

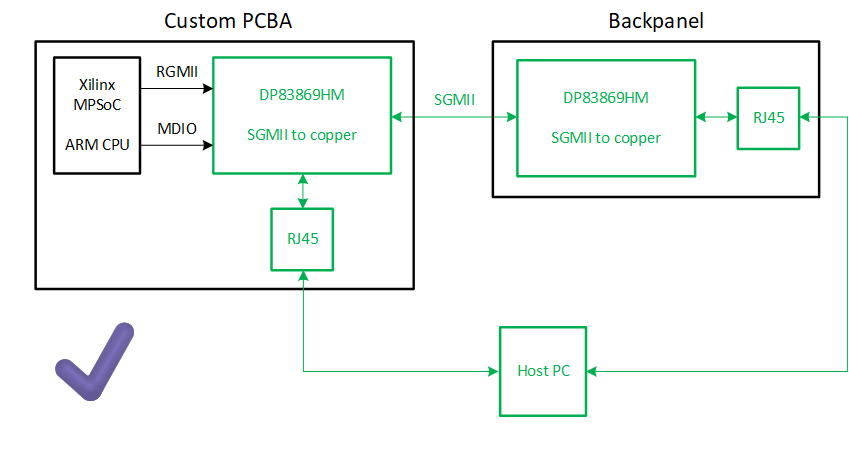

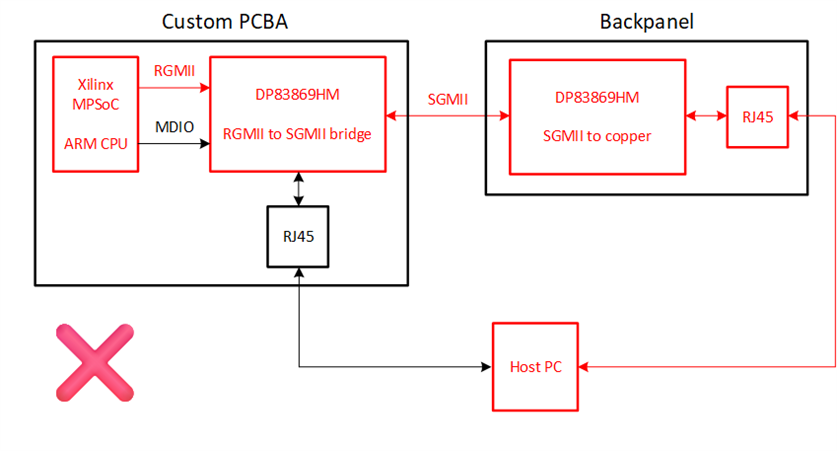

我们已经设置了定制 PCBA 和背板、两者都包含一个 DP83869HM PHY 芯片。 请参阅此方框图:

┌──────────────────────────────────────────┐ ┌──────────────────────────────┐ │ │ │ │ │ ┌──────────┐ ┌────────────────────┐ │ │ ┌───────────────┐ │ │ │ │RGMII │ │ │ │ │ │ ┌──────┐ │ │ │ Xilinx ├─────►│ DP83869HM │ │SGMII│ │ DP83869HM │ │ │ │ │ │ MPSoC │ │ ├─┼─────┤►│ ├──►│ RJ45 │ │ │ │ │MDIO │ │ │ │ │ │ │ │ │ │ │ ARM CPU ├─────►│RGMII to GMII bridge│ │ │ │SGMII to Copper│ └──────┘ │ │ │ │ │ │ │ │ │ │ │ │ └──────────┘ └────────────────────┘ │ │ └───────────────┘ │ │ Custom PCBA │ │ Backpanel │ └──────────────────────────────────────────┘ └──────────────────────────────┘

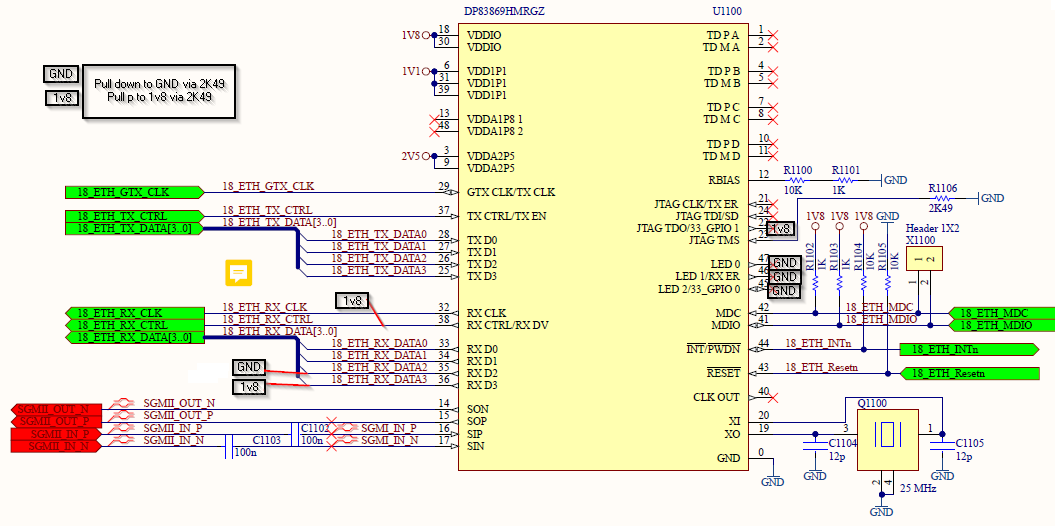

定制 PCBA 上的 PHY 通过 MDIO 和 RGMII 连接到 ARM CPU (Xilinx MPSoC 的一部分)。 背面板上的 PHY 根本未连接到 CPU、因此我们无法从 CPU 访问它、但已确认它工作正常。 定制 PCBA 上的 PHY 具有自举电阻器以在 RGMII 到 SGMII 桥接模式下工作、背板上的 PHY 具有自举电阻器以在 SGMII 到铜缆模式下工作。 我们将在 CPU 上运行 U-Boot 以配置 PHY。

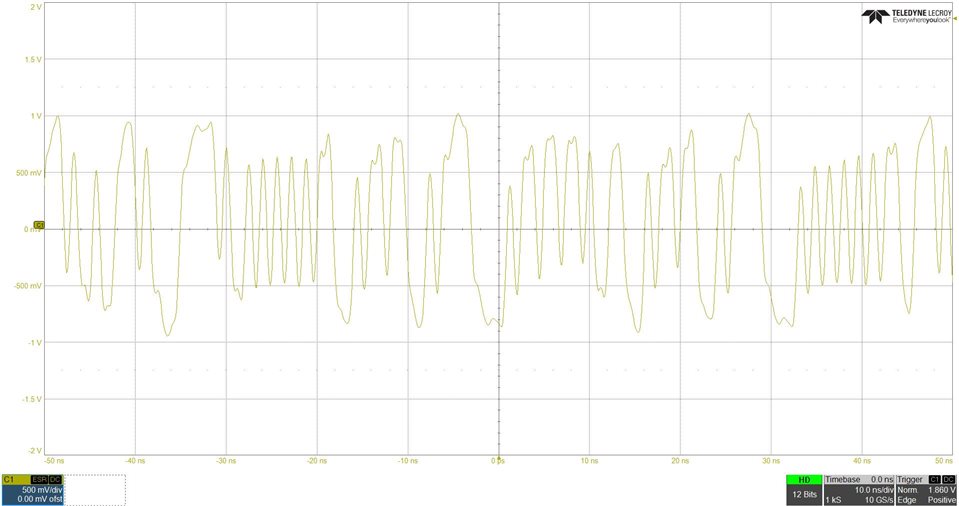

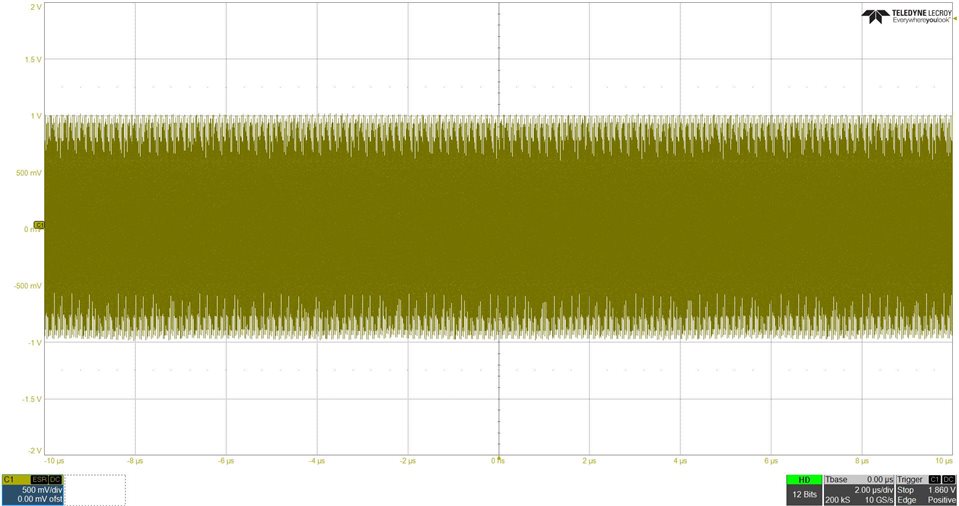

当我们 尝试从 ARM CPU 向主机 PC (连接到 RJ45)发送数据包时、它只会等待自动协商完成:

以太网@ff0c0000等待 PHY 自动协商完成……

寄存器0x1包含 0x7949、表示自动协商尚未完成。 不过、我们可以在主机 PC 上看到它已成功建立链路并且已完成自动协商。 寄存器0x6E 包含0x650、表明已为 RGMII 至 SGMII 桥配置了引导带寄存器、并禁用了 MIR_EN (RGMII 至 SGMII 桥接器需要此寄存器、如果为1、则会使用 SGMII 至 RGMII 桥接器)。 但是、当我们读取寄存器0x1DF 时、它会显示值0x43、其中 BRIDGE_MODE_RGMII_MAC 位设置为1、表示存在 SGMII 转 RGMII 桥接器。 数据表中似乎存在错误、因为第 9.4.8.4节说明了我们需要将0x43写入寄存器以获取 RGMII 转 SGMII 桥接器、但第 9.6.1.65节说明了 BRIDGE_MODE_RGMII_MAC (0x43中的4)必须为0。 尽管如此、两种模式目前都不适合我们。

在 PHY 的器件驱动程序中、我们已禁用其等待自动协商的部分(此 if 语句)、 然后、当我们将0x1DF 设置为0x43时、ARM CPU 会报告存在链路、当我们从 RJ45连接器断开主机 PC 的连接时、它也会报告不再存在链路。 但是、当它报告存在链路时、我们看不到主机 PC 上的 ARM CPU 发送的任何数据包。 当我们将0x1DF 设置为0x3时、它只会报告没有链路。 我们之所以进行此尝试、是因为我们不确定自定义 PCBA 上的 PHY 是否需要自动协商、因为这似乎已经由背板上的 PHY 管理。

在上述所有情况下、主机 PC 均显示成功链接。

我们的器件树配置如下所示:

&gem1 {

phy-mode = "rgmii-id";

phy-handle = <&phy0>;

status = "okay";

mdio: mdio@0 {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

reset-gpios = <&gpio 51 GPIO_ACTIVE_LOW>;

reset-assert-us = <100>;

reset-deassert-us = <280>;

phy0: ethernet-phy@05 {

#phy-cells = <1>;

status = "okay";

compatible = "ethernet-phy-ieee802.3-c45";

reg = <0x05>;

reset-gpios = <&gpio 51 GPIO_ACTIVE_LOW>;

reset-assert-us = <100>;

reset-deassert-us = <280>;

tx-fifo-depth = <0x1>;

rx-fifo-depth = <0x1>;

/* ti,op-mode = <0x03>; */

ti,max-output-impedance;

ti,clk-output-sel = <0x01>;

rx-internal-delay-ps = <2000>;

tx-internal-delay-ps = <2000>;

};

};

};

我们似乎已经竭尽所能来获得成功的链路和自动协商、但似乎没有效果。 我们还能做些什么呢?

此致、

罗伊·梅杰