主题中讨论的其他器件: TUSB1210

您好!

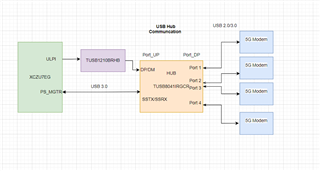

我们使用 连接到调制解调器的 TUSB8041IRGCR USB 集线器2.0和3.0。 我已经连接了我的硬件流。

在 lsusb 本身会检测到失败。 有时在 i2c1中、我们会获取从器件地址0x45。

您能对此提供帮助吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Brian、

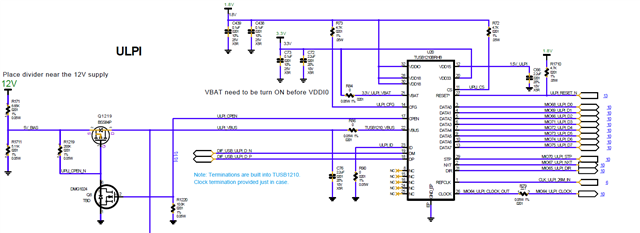

TUSB1210 原理图的下图

目前、我们的硬件设置涉及通过外部时钟发生器提供26 MHz REFCLK 来实现功能。 此外、ULPI 时钟输出60 MHz 时钟、该时钟连接到 FPGA 处理器的输入时钟。

但我有疑问:在器件树配置中、它被设置为仅主机模式。 在这种情况下、主机是否会生成60 MHz 时钟并将其提供给 ULPI IC 输入时钟、对吧?

我们提供了有关此问题的一些最新更新。 我们抽头了 ULPI (TUSB1210)和 USB 集线器(TUSB8041)之间的 DP 和 DN 线路、并连接了 USB A 型公连接器。 该器件随后连接到 PC、我们将 检测到 USB 集线器(TUSB8041)。 但我们注意到、1.1V 电源轨消耗的电流远高于数据表中提到的电流:

1.工作时、-421mA 在一系列370mA 之间消耗的电流、没有任何器件连接到 TUSB8041 IC。 从 PC 上移除 USB 公连接器时也能消耗相同的电流。

当 IC 工作时、我们尝试通过将 GRST 引脚与 GND 短接来重置 IC。 但电流处于300mA 范围内(根据数据表预计为28mA)。 执行此步骤后、IC 没有响应(仍然是消耗的电流为300mA)。 它仅在下电上电后才再次开始响应。

我们还尝试在 IC 开启时短接 GRST (带 GND)以复位 IC。 从1.1V 电源轨汲取的电流仍处于300mA 范围内。即使在复位释放后 IC 也没有响应、并且仅在下电上电后才开始工作。

这样做的原因是什么?

您好、Brian、

我们还提供了有关 ULPI 收发器(TUSB1210)的一些更新。 我们已移除复位信号处的上拉电阻器、并添加了如下所示的额外电路(AMD 建议使用该电路、该电路在复位释放后提供1ms 的切换脉冲)。 到目前为止可找到 ULPI 控制器、并且我们可访问 ULPI 寄存器。 我们还能够控制 CPEN 引脚。 我们也在 ULPI IC 的 DP DN 迹线上连接了一个笔式驱动器、在隔离 TUSB8041之后、不幸的是、这没有被检测到、并且我们不断收到一个称为"去抖失败"的错误。 我们还尝试获取寄存器转储、我们发现 ULPI 收发器处于器件模式。 这样做的原因是什么?