Other Parts Discussed in Thread: TSD05

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TSD05 您好、E2E 工程师、

我正在寻求您的专业知识、以审查专为在工业环境中提供强大 ESD 保护而设计的 PCB 布局。 以下是我的配置的详细信息:

- TVS 二极管 :TSD05,放置在靠近输入连接器的位置(2mm)。

- 信号特性 :4 x 5V 数字输入,最大频率~10kHz,迹线长度小于5cm。

- PCB 详细信息 :具有1.5mm FR4电介质的双层板。

-底层是直接连接到电源回路的实心接地。

-顶层在连接器附近有一个专用的 ESD 接地层,仅连接到 TVS 二极管接地引脚。

-此平面通过60微米铜层上大约40个通孔(0.35mm 钻孔,0.6mm 孔环)连接到底层接地层。 - 接地策略 :隔离式顶部 ESD 接地层用于在 ESD/EOS 事件期间充当缓冲器,将电荷分布在其区域内,以最大程度地减少对其他组件的影响。 PCB 上的所有 IC 都去耦。

- 跟踪详细信息 :输入到 TVS 二极管的线迹具有泪滴,最小宽度为0.6mm ;到 MCU 的线迹宽度为0.2mm ,标准间距为0.25mm。

- 滤波器元件 :在将输入信号传递到 MCU GPIO 引脚之前,RC 低通滤波器中的电阻器串联在靠近连接器的布线上。

我尚未进行任何测试、因此我特别想了解此布局的潜在问题、尤其是与 ESD 电流到 TVS 二极管和低通滤波器元件的分布有关的问题。

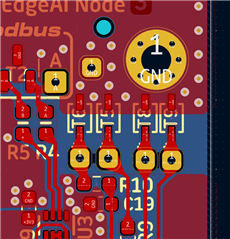

附件是顶层的布局、供您查看。 对于您可能提供的有关此布局是否建议以及任何潜在改进以增强 ESD 保护的任何指导或建议、我表示感谢。

感谢您的帮助!

我特别怀疑的是 ESD 电流分布模式以及朝向 TVS 二极管和 RC LP 滤波器元件的相对流量-非常感谢在这里提供任何指导。