请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83867E 您好、TI 团队、

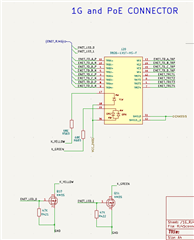

我们在 一个定制电路板应用中测试 DP83867ERGZT、这种定制电路板应用与千兆位以太网 MAC (GEM3)上的 Zynq FPGA MIO 连接。 这是系统中的唯一器件、LED 通过 LED_0和 LED_1引脚驱动。 芯片是否需要任何硬件搭接才能通过 MDI 总线进行响应?

协议:RGMII

(默认地址应保留为0x00、这是我所假设的、直到完成任何捆绑)