您好!

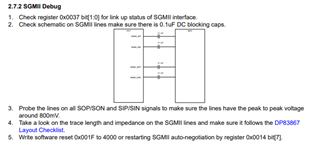

我们让 DP83867E SGMII EVM 通过 SGMII (6线)与 ultra96v2进行通信、 我们通过 MDIO 接口读取寄存器、但它无法对 PC 执行 ping 操作。

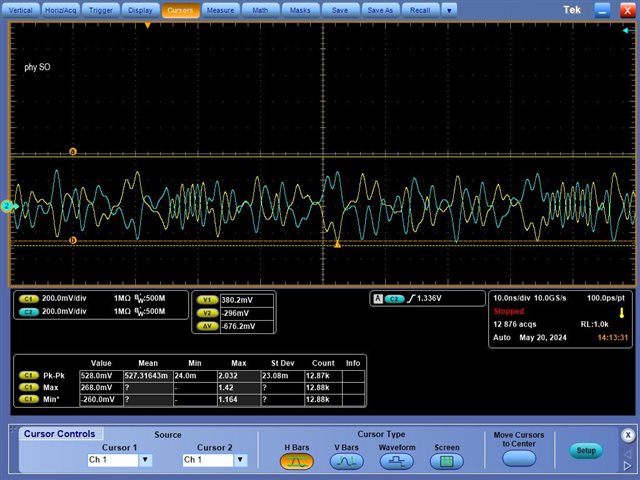

SGMII CAN 无信号。

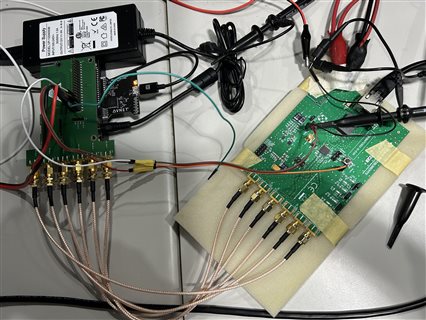

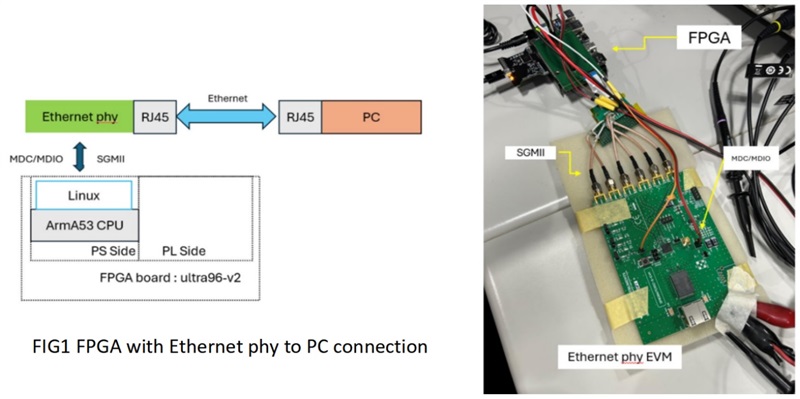

如图1所示。 当前使用带 Linux 的 ultra96v2 PS Side A53 CPU、并且我们想使用带 TI DP83867E PHY (DP83867E EVM)连接的 SGMII 模式。

现已确认以下情况:

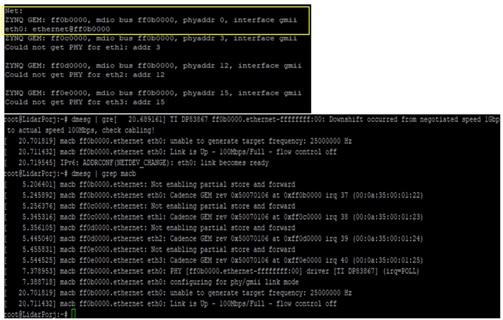

- Linux 引导检查:

FPGA FSBL 加载器可以初始以太网 phy (以太网@ff0b0000)、macb 驱动链路高达100m

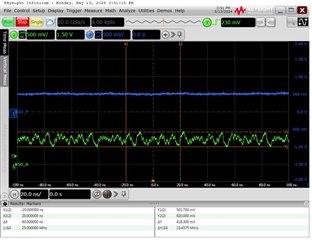

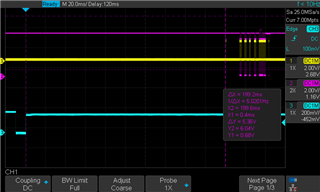

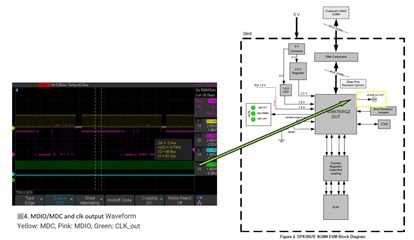

- 检查 MDIO/MDC 和 CLK 输出波形

黄色:MDC、粉色:MDIO、绿色:DP83867E CLK 输出

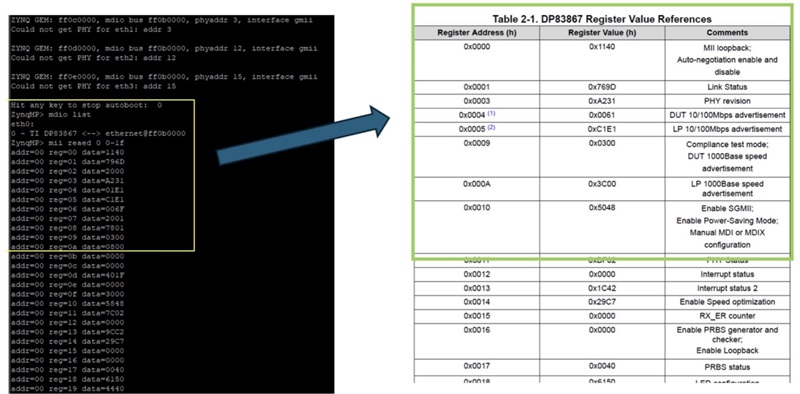

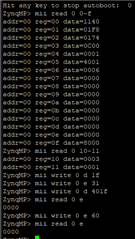

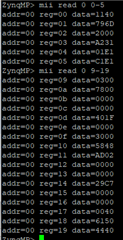

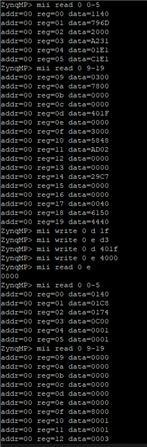

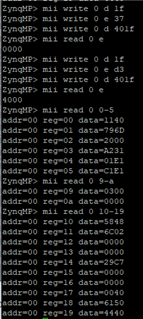

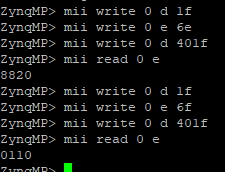

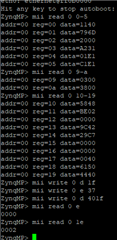

- uboot MII 检查

这是 MII 读取0-1f。 我不知道如何解决某些寄存器状态。

A. BMSR bit2 alway 0,我怎么能解决?

B. D3设置4000、但读取将为0000。 为什么可以设置 SGMII 6线模式?

c. CFG4 (addr 31 ): 0002