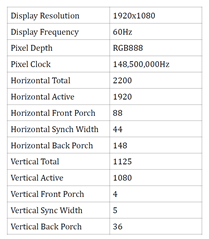

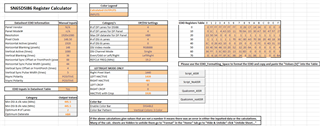

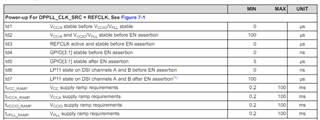

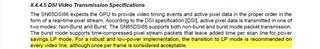

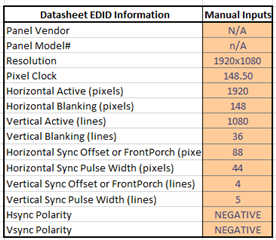

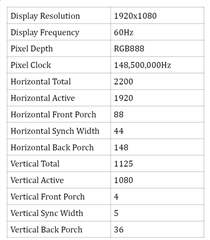

我们的 Xilinx Artix-7 FPGA 设计可生成两个1920 x 1080 MIPI 视频流。 每个流在进入 SN65DSI86芯片之前通过一个 Meticom MC20902芯片进行路由。 我们正在使用 TI 电子表格来为 SN65DSI86生成寄存器设置、并且我已经验证了寄存器中的定时值是正确的。 当 我们启用 SN65DSI86测试图形时、我们可以在外部监视器上看到来自 SN65DSI86的3840x1080显示端口视频。 但是、我们无法通过 SN65DSI86成功传输 DSI 视频。 在获得功能正常的 DSI 接口之前、我们仅在单通道模式下运行。 MIPI 流进行了建模、检查、看上去符合 SN65DSI86数据表、但是我们已经用这款器件努力了数周、未取得进展。 我们使用 Xilinx D-PHY IP 内核来操作 MIPI 接口、该内核由定制 DSI 接口驱动、该接口包含将 DSI 与视频帧同步输入同步的配置。 是否有一个 HDL 行为模型可用来帮助确定哪些内容会违反 SN65DSI86 DSI 接口? 另外、您能否指导我们前往在圣地亚哥地区以外运营的 FAE 寻求帮助? 如有任何其他可能有帮助的建议,将不胜感激。